- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373102 > KAC-1310 (Electronic Theatre Controls, Inc.) 1280 (H) x 1024 (V) SXGA CMOS Image Sensor PDF資料下載

參數(shù)資料

| 型號(hào): | KAC-1310 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 1280 (H) x 1024 (V) SXGA CMOS Image Sensor |

| 中文描述: | 1280(高)x 1024(五)SXGA CMOS圖像傳感器 |

| 文件頁數(shù): | 55/76頁 |

| 文件大小: | 759K |

| 代理商: | KAC-1310 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

IMAGE SENSOR SOLUTIONS

55

IMAGE SENSOR SOLUTIONS

K A C - 1 3 1 0 R e v 4 w w w . k o d a k . c o m / g o / i m a g e r s 5 8 5 - 7 2 2 - 4 3 8 5 E m a i l : i m a g e r s @ k o d a k . c o m

Capture Mode Control (40

h

)

The Capture Mode Control Register defines how

the data is captured and how the data is to be

provided at the output. Setting the

cms

bit will

stop the current CFRS output data stream at the

end of the current frame and place the imager in

Single Frame Capture Mode (SFRS). While the

cms

bit is set (SFRS), the output of frames can be

paused with the TRIGGER input pin. When the

TRIGGER pin is low (V

SS

) the output of frames is

suspended. When the TRIGGER pin is high (V

DD

)

frames are continuous. The default for

cms

is 0

(CFRS). In CFRS the frames are continuously

output and the TRIGGER pin is ignored. The

Frame Rate is slightly reduced when the

cms

is

set (SFRS) because care is taken in the startup

such that the first frame output is valid. This

causes a slight delay at the start of each frame.

See

Figure 22

on

page

32

for a timing diagram for

SFRS mode. With the

cms

low(=0), the Frame

Rate is faster, but the first frame will be invalid

(wrong integration time).

Address

40

h

When the

hm

bit is set, the HCLK sync is high

whenever valid WOI pixel data is being clocked

out and low during the other blanking intervals.

The HCLK does NOT toggle at the MCLK rate

when the

hm

bit is set. When

hm

is set the HCLK

will go high once at the beginning of the valid pixel

data and remain high until the last WOI pixel has

been clocked out. When the

hm

bit is set the

he

bit is ignored. The

sp

bit is used to define whether

SOF is active high or low. SOF is active high by

default. The

ve

bit is used to determine whether

VCLK is output at the beginning of the virtual

frame rows or only for the WOI rows. The

ve

bit

defaults to VCLK on WOI rows only. The

vp

bit is

used to define whether VCLK is active high(the

default) or active low. The

he

bit is used to

determine whether HCLK is output continuously

(needed for some frame grabbers) or only for

pixels within the WOI (default). The

hp

bit is used

to define whether HCLK is active high (default) or

low.

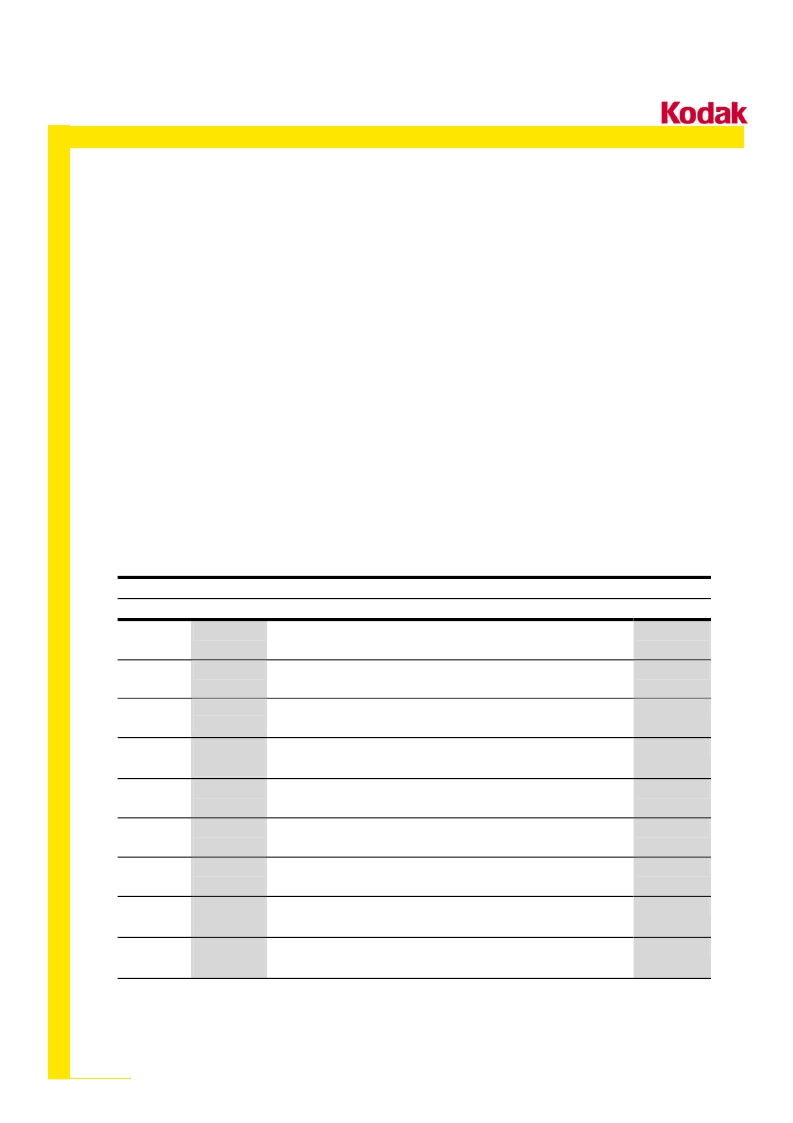

Capture Mode Control

Default

2A

h

7 (msb)

6

5

4

3

2

1

0 (lsb)

FUO

cms

sp

ve

vp

he

hp

hm

Bit

Number

Function

Description

Reset

State

7

FUO

Factory Use Only

0

b

6

RSCM

Mode

0

b

= Continuous Frame Rolling Shutter (CFRS)

1

b

= Single Frame Rolling Shutter (SFRS)

0

b

5

SOF

Phase

0

b

= SOF sync active low

1

b

= SOF sync active high

1

b

4

VCLK

Enable

0

b

= VCLK Sync on WOI rows only

1

b

= VCLK Sync on WOI and Virtual Rows

0

b

3

VCLK

Phase

0

b

= Active low

1

b

= Active high

1

b

2

HCLK

Enable

0

b

= Pixel sync on WOI pixels only

1

b

= Continuous pixel sync

0

b

1

HCLK

Phase

0

b

= Active low

1

b

= Active high

1

b

0

HCLK

Mode

0

b

= Toggles - Toggles at MCLK rates defined by (he) bit

1

b

= Continuous - Pixel Valid Envelope

0

b

Table 27: Capture Mode Register (40

h

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KAF-1001E | 1024(H) x 1024(V) Pixel Enhanced Response Full-Frame CCD Image Sensor Performance Specification |

| KAF-1602E | Replacement for Texas Instruments part number SN74LS164N. Buy from authorized manufacturer Rochester Electronics. |

| KaLNA3S.04R | Ka Band Low Noise Amplifier(工作頻率從33GHz到36GHz的低噪聲Ka波段功率放大器) |

| KAQW214 | PHOTO MOS RELAYS |

| KAQW414A | HIGH VOLTAGE, PHOTO MOS RELAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KAC-15 | 功能描述:保險(xiǎn)絲 600V 15A Semiconductor RoHS:否 制造商:Littelfuse 產(chǎn)品:Surface Mount Fuses 電流額定值:0.5 A 電壓額定值:600 V 保險(xiǎn)絲類型:Fast Acting 保險(xiǎn)絲大小/組:Nano 尺寸:12.1 mm L x 4.5 mm W 安裝風(fēng)格: 端接類型:SMD/SMT 系列:485 |

| KAC-150 | 功能描述:保險(xiǎn)絲 600V 150A Semiconductor RoHS:否 制造商:Littelfuse 產(chǎn)品:Surface Mount Fuses 電流額定值:0.5 A 電壓額定值:600 V 保險(xiǎn)絲類型:Fast Acting 保險(xiǎn)絲大小/組:Nano 尺寸:12.1 mm L x 4.5 mm W 安裝風(fēng)格: 端接類型:SMD/SMT 系列:485 |

| KAC-17.5 | 制造商:COOPER 制造商全稱:Cooper Bussmann, Inc. 功能描述:High Speed Fuses |

| KAC-17-1/2 | 功能描述:保險(xiǎn)絲 600V 17.5A Semiconductor RoHS:否 制造商:Littelfuse 產(chǎn)品:Surface Mount Fuses 電流額定值:0.5 A 電壓額定值:600 V 保險(xiǎn)絲類型:Fast Acting 保險(xiǎn)絲大小/組:Nano 尺寸:12.1 mm L x 4.5 mm W 安裝風(fēng)格: 端接類型:SMD/SMT 系列:485 |

| KAC-17-1-2 | 制造商:Cooper Bussmann 功能描述:FUSE 17.5A 600V 2PIN - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。