- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360998 > ISP1181 (NXP Semiconductors N.V.) Full-speed Universal Serial Bus Interface Device(全速通用串行總線接口器件) PDF資料下載

參數(shù)資料

| 型號(hào): | ISP1181 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Full-speed Universal Serial Bus Interface Device(全速通用串行總線接口器件) |

| 中文描述: | 全速通用串行總線接口設(shè)備(全速通用串行總線接口器件) |

| 文件頁(yè)數(shù): | 27/69頁(yè) |

| 文件大?。?/td> | 1655K |

| 代理商: | ISP1181 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)

Philips Semiconductors

ISP1181

Full-speed USB interface

Objective specification

Rev. 01 — 13 March 2000

27 of 69

9397 750 06896

Philips Electronics N.V. 2000. All rights reserved.

Code (Hex): B8/B9 —

write/read Mode Register

Transaction —

write/read 1 byte

[1]

Unchanged by a bus reset.

12.1.4

Write/Read Hardware Configuration

This command is used to access the Hardware Configuration Register, which

consists of 2 bytes. The first (lower) byte contains the device configuration and

control values, the second (upper) byte holds the clock control bits and the clock

division factor. The bit allocation is given in

Table 22

. A bus reset will not change any

of the programmed bit values.

The Hardware Configuration Register controls the connection to the USB bus, clock

activity and power supply during ‘suspend’ state, output clock frequency, DMA

operating mode and pin configurations (polarity, signalling mode).

Code (Hex): BA/BB —

write/read Hardware Configuration Register

Transaction —

write/read 2 bytes

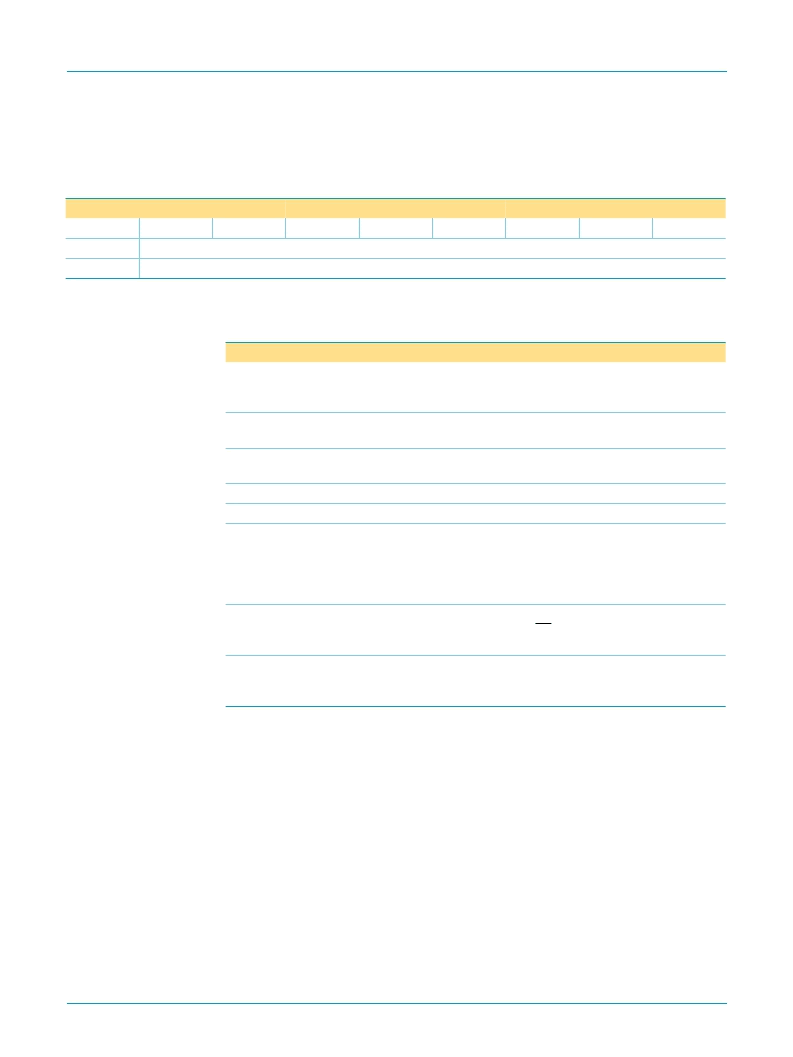

Table 20: Mode Register: bit allocation

Bit

7

Symbol

DMAWD

Reset

0

[1]

Access

R/W

6

5

4

3

2

1

0

SNDRSU

0

R/W

GOSUSP

0

R/W

reserved

0

R/W

INTENA

0

[1]

R/W

DBGMOD

0

[1]

R/W

DISGLBL

0

[1]

R/W

SOFTCT

0

[1]

R/W

Table 21: Mode Register: bit description

Bit

Symbol

7

DMAWD

Description

A logic 1 selects 16-bit DMA bus width (bus configuration modes

0 and 2). A logic 0 selects 8-bit DMA bus width. Bus reset value:

unchanged.

Writing a logic 1 followed by a logic 0 will generate an upstream

‘resume’ signal of 10 ms duration, after a 5 ms delay.

Writing a logic 1 followed by a logic 0 will activate ‘suspend’

mode.

reserved

A logic 1 enables all interrupts. Bus reset value: unchanged.

A logic 1 enables debug mode. where all NAKs and errors will

generate an interrupt. A logic 0 selects normal operation, where

interrupts are generated on every ACK (bulk endpoints) or after

every data transfer (isochronous endpoints). Bus reset value:

unchanged.

A logic 1 disables GoodLInk LED blinking on USB traffic. The

LED will be continuously on (GL = LOW) after successful

enumeration. Bus reset value: unchanged.

A logic 1 enables SoftConnect (see

Section 7.4

). This bit is

ignored if EXTPUL = 1 in the Hardware Configuration Register

(see

Table 22

). Bus reset value: unchanged.

6

SNDRSU

5

GOSUSP

4

3

2

-

INTENA

DBGMOD

1

DISGLBL

0

SOFTCT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP1181DGG | INDUCTOR 4.7NH +-.3NH 0402 SMD |

| ISP1183 | Low-power Universal Serial Bus interface device with DMA |

| ISP1183BS | Low-power Universal Serial Bus interface device with DMA |

| ISP1301 | Universal Serial Bus On-The-Go transceiver |

| ISP1301BS | Universal Serial Bus On-The-Go transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1181A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus peripheral controller |

| ISP1181ABS | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus peripheral controller |

| ISP1181ABS,518 | 功能描述:USB 接口集成電路 USB 1.1 ADV DEVICE RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1181ABS,551 | 功能描述:USB 接口集成電路 USB 1.1 ADVANCED DEVICE RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1181ABS,557 | 功能描述:USB 接口集成電路 DO NOT USE ORDER -S OR -T PART RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。