- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16261 > DS3112DK (Maxim Integrated Products)KIT DEMO FOR DS3112 PDF資料下載

參數(shù)資料

| 型號(hào): | DS3112DK |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 132/133頁 |

| 文件大小: | 0K |

| 描述: | KIT DEMO FOR DS3112 |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 主要目的: | 接口,交叉點(diǎn)開關(guān)/多路復(fù)用器 |

| 已用 IC / 零件: | DS3112 |

| 已供物品: | 板,CD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁當(dāng)前第132頁第133頁

DS3112

98 of 133

10.2 FEAC Status Register Description

Register Name:

FSR

Register Description:

FEAC Status Register

Register Address:

92h

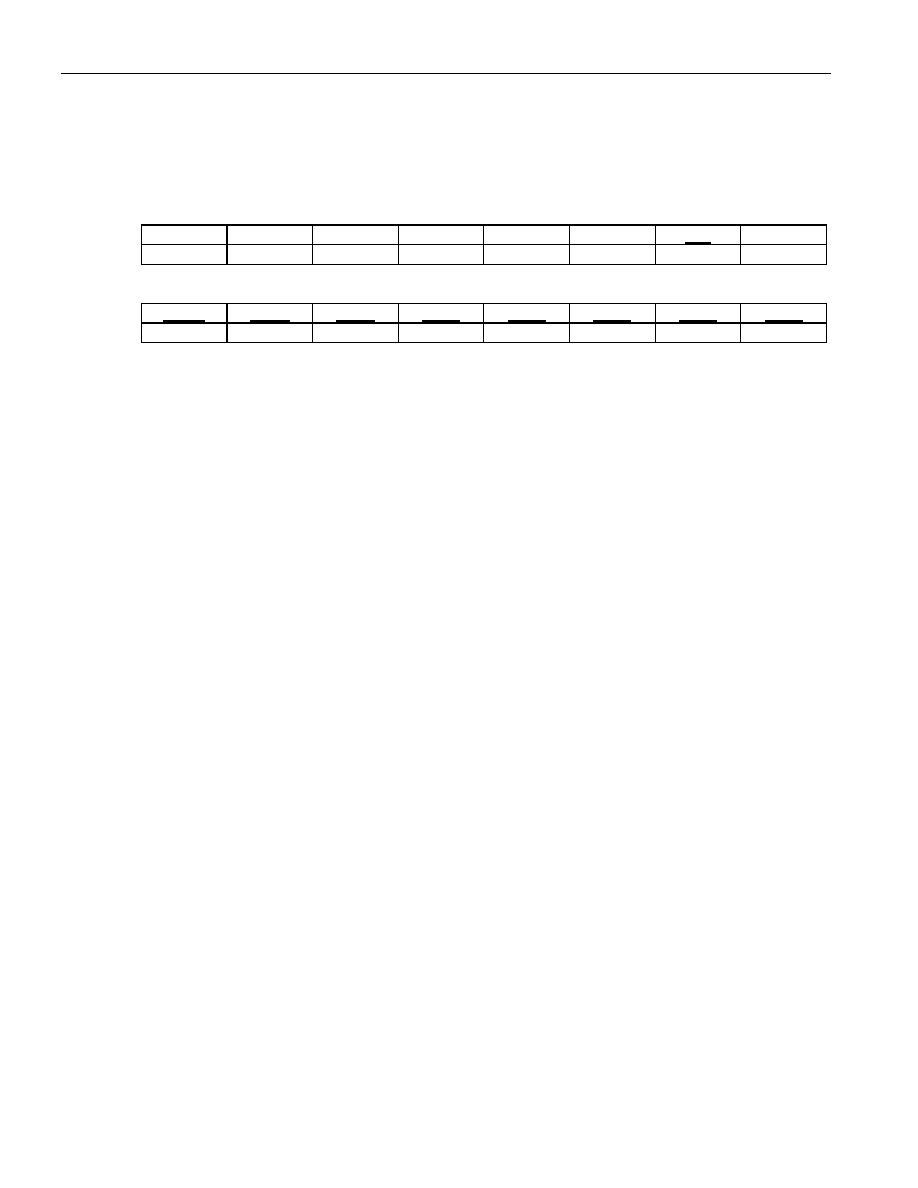

Bit #

7

6

5

4

3

2

1

0

Name

—

RFI

RFCD

Default

—

Bit #

15

14

13

12

11

10

9

8

Name

RFFO

RFFE

RFF5

RFF4

RFF3

RFF2

RFF1

RFF0

Default

—

Note: Bits that are underlined are read-only; all other bits are read-write.

Bit 0: Receive FEAC Codeword Detected (RFCD). This latched read-only event-status bit will be set to a one

each time the FEAC controller has detected and validated a new FEAC codeword. This bit will be cleared when

read and will not be set again until another new codeword is detected. The setting of this bit can cause a hardware

interrupt to occur if the FEAC bit in the Interrupt Mask for MSR (IMSR) register is set to a one. The interrupt will

be allowed to clear when this bit is read.

Bit 14: Receive FEAC FIFO Empty (RFFE). This read-only real time status bit will be set to a one when the

Receive FEAC FIFO is empty and hence the RFF0 to RFF5 bits contain no valid information.

Bit 1: Receive FEAC Idle (RFI). This latched read-only event status bit will be set to a one each time the FEAC

controller has detected 16 consecutive ones following a valid codeword. This bit will be cleared when read. The

setting of this bit can cause a hardware interrupt to occur if the IERFI bit in the FEAC Control Register (FCR) is

set to one and the FEAC bit in the Interrupt Mask for MSR (IMSR) is set to one.

Bits 8 to 13: Receive FEAC FIFO Data (RFF0 to RFF5). Data from the Receive FEAC FIFO can be read from

these bits. The FEAC codeword is of the form ...0xxxxxx011111111... where the rightmost bit is received first.

These six bits are the debounced and integrated middle six bits of the second byte of the FEAC codeword (i.e., the

six “x” bits). RFF0 is the LSB and is received first while RFF5 is the MSB and is received last.

Bit 15: Receive FEAC FIFO Overflow (RFFO). This latched read-only event-status bit will be set to a one when

the receive FEAC controller has attempted to write to an already full Receive FEAC FIFO and current incoming

FEAC codeword is lost. This bit will be cleared when read and will not be set again until another FIFO overflow

occurs (i.e., the Receive FEAC FIFO has been read and then fills beyond capacity).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RMM10DSEN | CONN EDGECARD 20POS .156 EYELET |

| DS2148DK | KIT DESIGN LIU DS2148 3/5V T1/E1 |

| H3CWH-6436G | IDC CABLE - HKC64H/AE64G/HPL64H |

| 78M6618-PDU-1 | EVAL KIT DS8005 |

| RMM10DSEH | CONN EDGECARD 20POS .156 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3112N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC TEMPE T3/E3 MUX FRMR & M13/E13/G.747 MUX RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3112N+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC TEMPE T3/E3 MUX FRMR & M13/E13/G.747 MUX RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3112N+W | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC TEMPE T3/E3 MUX FRMR & M13/E13/G.747 MUX RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3112NC1 | 制造商:Maxim Integrated Products 功能描述:T3 E3 MULTIPLEXER, 3.3V T3/E3 FRAMER AND M13/E13/G.747 MUX - Rail/Tube |

| DS3112ND1E | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。