- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375384 > AX88790L (ASIX Electronics Corporation) 10/100BASE 3-in-1 PCMCIA Fast Ethernet Controller PDF資料下載

參數(shù)資料

| 型號: | AX88790L |

| 廠商: | ASIX Electronics Corporation |

| 英文描述: | 10/100BASE 3-in-1 PCMCIA Fast Ethernet Controller |

| 中文描述: | 一個10/100Base 3合1的PCMCIA快速以太網(wǎng)控制器 |

| 文件頁數(shù): | 28/60頁 |

| 文件大小: | 633K |

| 代理商: | AX88790L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

ASIX ELECTRONICS CORPORATION

28

AX88790 L 3-in-1 PCMCIA Fast Ethernet Controller

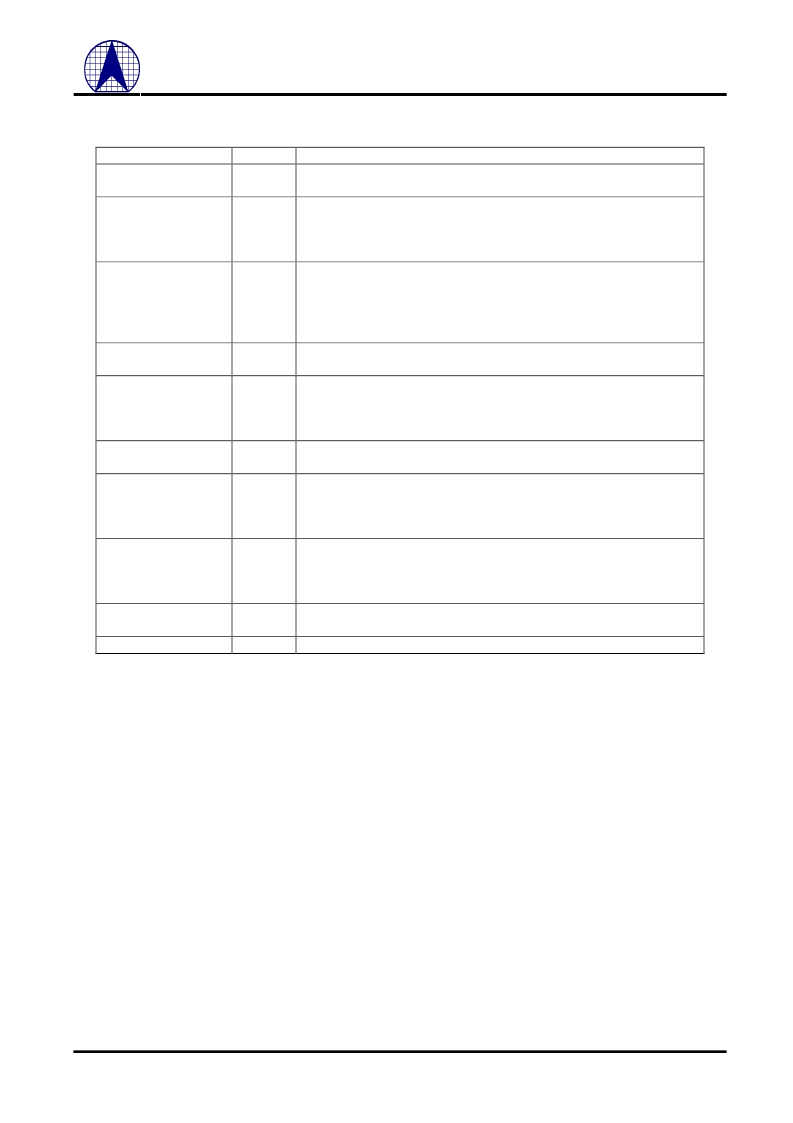

4.4.1 MR0 -- Control Register Bit Descriptions

FIELD

TYPE

0.15 (SW_RESET)

R/W

DESCRIPTION

Reset.

Setting this bit to a 1 will reset the PHY. All registers will be set to

their default state. This bit is self-clearing. The default is 0.

Loopback.

When this bit is set to 1, no data transmission will take place on

the media. Any receive data will be ignored. The loopback signal path will

contain all circuitry up to, but not including, the PMD. The default value is

a 0.

Speed Selection.

The value of this bit reflects the current speed of operation

(1 =100 Mbits/s; 0 =10 Mbits/s). This bit will only affect operating speed

when the autonegotiation enable bit (register 0, bit 12) is disabled (0). This

bit is ignored when autonegotiation is enabled (register 0, bit 12). This bit is

ANDed with the SPEED_PIN signal.

Autonegotiation Enable.

The autonegotiation process will be enabled by

set-ting this bit to a 1. The default state is a 1.

Powerdown.

The PHY may be placed in a low-power state by setting this bit

to a 1, both the 10Mbits/s transceiver and the 100Mbits/s transceiver will be

powered down. While in the powerdown state, the PHY will respond to

management transactions. The default state is a 0.

Isolate.

When this bit is set to a 1, the MII outputs will be brought to the

high-impedance state. The default state is a 0.

Restart Autonegotiation.

Normally, the autonegotiation process is started

at powerup. Setting this bit to a 1 may restart the process. The default state is

a 0. The NWAYDONE bit (register 1, bit 5) is reset when this bit goes to a

1. This bit is self-cleared when autonegotiation restarts.

Duplex Mode.

This bit reflects the mode of operation (1 = full duplex; 0 =

half duplex). This bit is ignored when the autonegotiation enable bit

(register 0, bit 12) is enabled. The default state is a 0. This bit is ORed with

the F_DUP pin.

Collision Test.

When this bit is set to a 1, the PHY will assert the MCOL

signal in response to MTX_EN.

Reserved.

All bits will read 0.

0.14 (LOOPBACK)

R/W

0.13(SPEED100)

R/W

0.12 (NWAY_ENA)

R/W

0.11 (PWRDN)

R/W

0.10 (ISOLATE)

R/W

0.9 (REDONWAY)

R/W

0.8 (FULL_DUP)

R/W

0.7 (COLTST)

R/W

0.6:0 (RESERVED)

NA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AX88796BLF | IC,MC14411P |

| AX88796BLI | Low-pin-count Non-PCI 8/16-bit 10/100M Fast Ethernet Controller |

| AX88872P | 10/100BASE Dual Speed “Swipeater” Controller |

| AX9902MS | 2N and 2P-Channel Enhancement Mode Power MOSFET |

| AX9902MSA | 2N and 2P-Channel Enhancement Mode Power MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AX88796 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3-in-1 Local Bus Fast Ethernet Controller |

| AX88796ALF | 制造商:ASIX 功能描述:10/100 MAC,COMMERCIAL 128PIN |

| AX88796BLF | 制造商:Asix Electronics 功能描述:IEEE802.3 / IEEE802.3u LAN standard Ethernet 3.3V 64LQFP Tray 制造商:ASIX 功能描述:10/100 MAC,COMMERCIAL 64PIN |

| AX88796BLI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:High-Performance Non-PCI Single-Chip 8/16 bit 10/100M Fast Ethernet Controller |

| AX88796C | 制造商:ASIX 制造商全稱:ASIX 功能描述:Low-Power SPI or Non-PCI Ethernet Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。