- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374035 > ADSP-2173 (Analog Devices, Inc.) DSP Microcomputer(DSP 微計(jì)算機(jī)) PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-2173 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | DSP Microcomputer(DSP 微計(jì)算機(jī)) |

| 中文描述: | 微機(jī)的DSP(數(shù)字信號(hào)處理器微計(jì)算機(jī)) |

| 文件頁(yè)數(shù): | 15/52頁(yè) |

| 文件大?。?/td> | 685K |

| 代理商: | ADSP-2173 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

ADSP-2171/ADSP-2172/ADSP-2173

REV. A

–15–

Control Registers

INST RUCT ION SE T DE SCRIPT ION

T he ADSP-217x assembly language instruction set has an alge-

braic syntax that was designed for ease of coding and read-

ability. T he assembly language, which takes full advantage of

the processor’s unique architecture, offers the following benefits:

T he algebraic syntax eliminates the need to remember cryptic

assembler mnemonics. For example, a typical arithmetic add

instruction, such as AR = AX 0 + AY0, resembles a simple

equation.

Every instruction assembles into a single, 24-bit word that can

execute in a single instruction cycle.

T he syntax is a superset ADSP-2100 Family assembly lan-

guage and is completely source and object code compatible

with other family members. Programs may need to be relo-

cated to utilize internal memory and conform to the ADSP-

217x’s interrupt vector and reset vector map.

Sixteen condition codes are available. For conditional jump,

call, return, or arithmetic instructions, the condition can be

checked and the operation executed in the same instruction

cycle.

Multifunction instructions allow parallel execution of an arith-

metic instruction with up to two fetches or one write to pro-

cessor memory space during a single instruction cycle.

Consult the

ADSP-2100 Family User’s Manual

for a complete

description of the syntax and an instruction set reference.

Biased Rounding

A new mode allows biased rounding in addition to the normal

unbiased rounding. When the BIASRND bit is set to 0, the nor-

mal unbiased rounding operations occur. When the BIASRND

bit is set to 1, biased rounding occurs instead of the normal un-

biased rounding. When operating in biased rounding mode all

rounding operations with MR0 set to 0x8000 will round up,

rather than only rounding odd MR1 values up. For example:

MR value before RND

00-0000-8000

00-0001-8000

00-0000-8001

00-0001-8001

00-0000-7FFF

00-0001-7FFF

T his mode only has an effect when the MR0 register contains

0x8000, all other rounding operation work normally. T his mode

was added to allow more efficient implementation of bit speci-

fied algorithms which specify biased rounding such as the GSM

speech compression routines. Unbiased rounding is preferred

for most algorithms.

Note:

BIASRND bit is Bit 12 of the SPORT 0 Autobuffer

Control register.

biased RND result

00-0001-8000

00-0002-8000

00-0001-8001

00-0002-8001

00-0000-7FFF

00-0001-7FFF

unbiased RND result

00-0000-8000

00-0002-8000

00-0001-8001

00-0002-8001

00-0000-7FFF

00-0001-7FFF

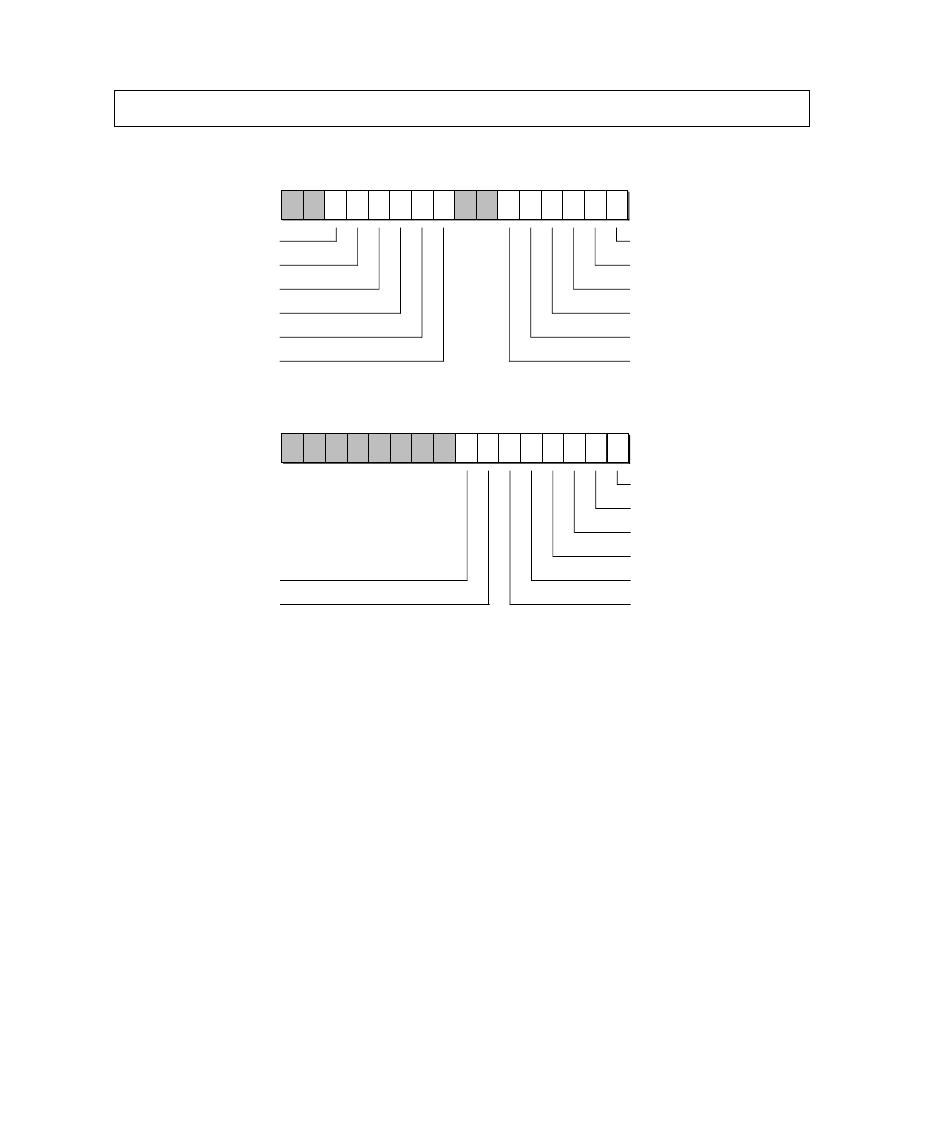

HSR6

0x3FE6

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Host HDR0 Write

Host HDR1 Write

Host HDR2 Write

Host HDR3 Write

Host HDR4 Write

Host HDR5 Write

2171 HDR5 Write

2171 HDR4 Write

2171 HDR3 Write

2171 HDR2 Write

2171 HDR1 Write

2171 HDR0 Write

Overwrite Mode

Software Reset

HSR7

0x3FE7

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

2171 HDR0 Write

2171 HDR1 Write

2171 HDR2 Write

2171 HDR3 Write

2171 HDR4 Write

2171 HDR5 Write

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-2181BS-115 | DSP Microcomputer |

| ADSP-2181BS-133 | DSP Microcomputer |

| ADSP-2181KS-115 | DSP Microcomputer |

| ADSP-2181KS-133 | DSP Microcomputer |

| ADSP-2181KS-160 | DSP Microcomputer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2173BS-80 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-2173BST-80 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 20MHz 20MIPS 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:16BIT FXD PT PROC 3.3V - Bulk |

| ADSP-2176-760040 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760061 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760243 | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。