- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375249 > AD9865BCPZ1 (Analog Devices, Inc.) Broadband Modem Mixed-Signal Front End PDF資料下載

參數(shù)資料

| 型號: | AD9865BCPZ1 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Broadband Modem Mixed-Signal Front End |

| 中文描述: | 寬帶調(diào)制解調(diào)器混合信號前端 |

| 文件頁數(shù): | 20/48頁 |

| 文件大小: | 1672K |

| 代理商: | AD9865BCPZ1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

AD9865

Rev. A | Page 20 of 48

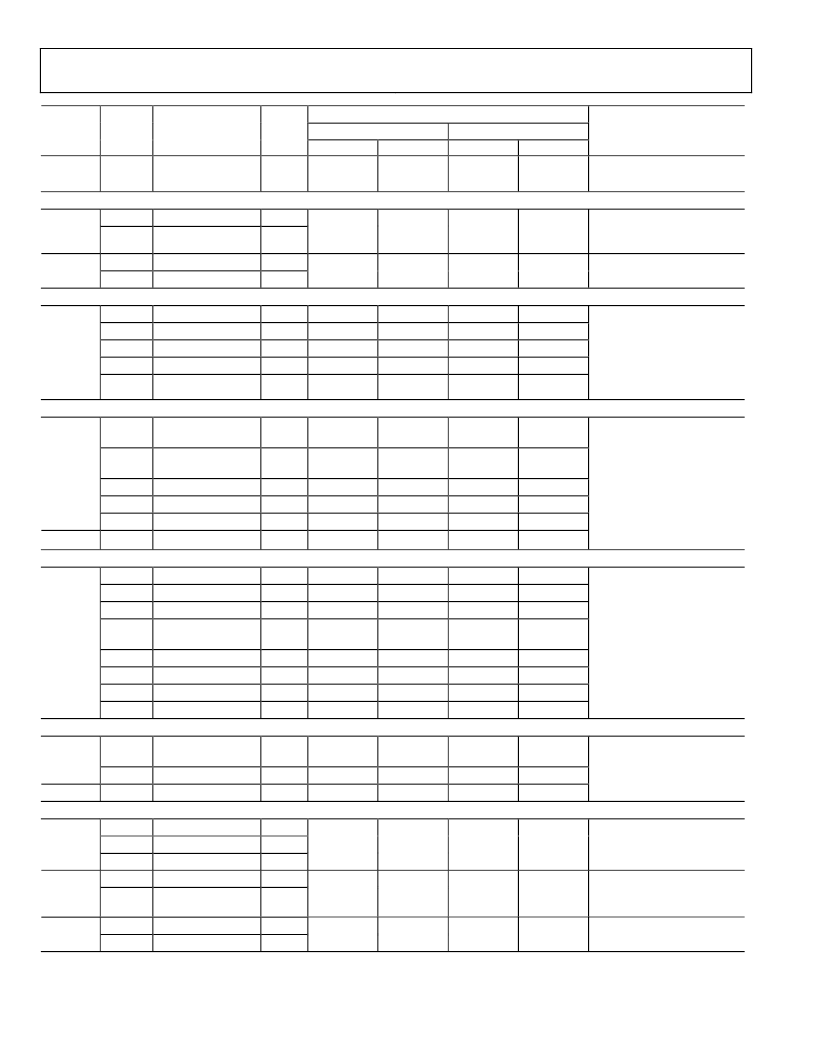

Power-Up Default Value

MODE = 0 (Half-Duplex)

CONFIG = 0

MODE = 1 (Full-Duplex)

CONFIG = 0

Address

(Hex)

1

0x08

Bit

Break-

down

(7:0)

Description

Rx Filter Tuning

Cut-off Frequency

Width

8

CONFIG = 1

CONFIG = 1

Comments

Refer to Low-Pass Filter

section.

0x80

0x61

0x80

0x80

Tx/Rx PATH GAIN CONTROL

0x09

(6)

(5:0)

Use SPI Rx Gain

Rx Gain Code

1

6

0x00

0x00

0x00

0x00

Default setting is for

hardware Rx gain code via

PGA or Tx data port.

Default setting is for Tx gain

code via SPI control.

0x0A

Tx AND Rx PGA CONTROL

0x0B

(6)

(5)

(3)

(2)

(1)

(6)

(5:0)

Use SPI Tx Gain

Tx Gain Code

1

6

0x7F

0x7F

0x7F

0x7F

PGA Code for Tx

PGA Code for Rx

Force GAIN strobe

Rx Gain on Tx Port

3-Bit RxPGA Port

1

1

1

1

1

0

1

0

0

0

0

1

0

0

1**

0

1

0

1*

0

0

1

0

1*

0

Default setting is RxPGA

control active.

*Tx port with GAIN strobe

(AD9875/AD9876-compatible).

** 3-bit RxPGA gain map

(AD9975-compatible).

Tx DIGITAL FILTER AND INTERFACE

0x0C

(7:6)

Interpolation

Factor

Invert

TXEN/TXSYNC

Tx 5/5 Nibble*

LS Nibble First*

TXCLK neg. edge

Twos complement

2

01

00

01

01

(4)

1

0

0

0

0

Rx INTERFACE AND ANALOG/DIGITAL LOOPBACK

0x0D

(7)

Analog Loopback

(6)

Digital Loopback*

(5)

Rx Port 3-State

(4)

Invert

RXEN/RXSYNC

(3)

RX 5/5 Nibble

(2)

LS Nibble First*

(1)

RXCLK neg. edge

(0)

Twos complement

DIGITAL OUTPUT DRIVE STRENGTH, TxDAC OUTPUT, AND REV ID

0x0E

(7)

Low Drive

Strength

(0)

TxDAC Output

0x0F

(3:0)

REV ID Number

Tx IAMP GAIN AND BIAS CONTROL

0x10

(7)

Select Tx Gain

(6:4)

G1

(2:0)

N

0x11

(6:4)

G2

(2:0)

G3

(3)

(2)

(1)

(0)

1

1

1

1

N/A

N/A

0

0

N/A

N/A

0

0

0

0

0

1

0

0

0

1

Default setting is 2×

interpolation with LPF

response. Data format is

straight binary for half-

duplex and twos

complement for full-duplex

interface.

*Full-duplex only.

1

1

1

1

0

0

N/A

0

0

0

N/A

0

0

0

0

0

0

0

0

0

1

1

1

1

N/A

N/A

0

0

N/A

N/A

0

0

0

0

0

1

0

0

0

1

Data format is straight

binary for half-duplex and

twos complement for full-

duplex interface.

Analog loopback: ADC Rx

data fed back to TxDAC.

Digital loopback: Tx input

data to Rx output port.

*Full-duplex only.

1

0

0

0

0

1

4

0

0x00

0

0x00

0

0x00

0

0x00

Default setting is for high

drive strength and IAMP

enabled.

1

3

3

3

3

0x44

0x44

0x44

0x44

Secondary path G1 = 0, 1, 2,

3, 4.

Primary path N = 0, 1, 2, 3, 4.

0x62

0x62

0x62

0x62

Secondary path stages:

G2 = 0 to 1.50 in 0.25 steps

and G3 = 0 to 6.

Standing current of primary

and secondary path.

0x12

(6:4)

(2:0)

Stand_Secondary

Stand_Primary

3

3

0x01

0x01

0x01

0x01

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9865BCPZRL1 | Broadband Modem Mixed-Signal Front End |

| AD9865CHIPS | Broadband Modem Mixed-Signal Front End |

| AD9887 | Dual Interface for Flat Panel Displays |

| AD9888 | 100/140/170/205 MSPS Analog Flat Panel Interface |

| AD9888KS-100 | 100/140/170/205 MSPS Analog Flat Panel Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9865BCPZRL | 功能描述:IC PROCESSOR FRONT END 64LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應(yīng)商設(shè)備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9865BCPZRL1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9865CHIPS | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9865-EB | 制造商:Analog Devices 功能描述:MODEM, BROADBAND MODEM MIXED SGNL FRONT END - Bulk |

| AD9866 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。