- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375249 > AD9865BCPRL (ANALOG DEVICES INC) Broadband Modem Mixed-Signal Front End PDF資料下載

參數(shù)資料

| 型號: | AD9865BCPRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Broadband Modem Mixed-Signal Front End |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, QCC64 |

| 封裝: | MO-220-VMMD, LFCSP-64 |

| 文件頁數(shù): | 6/48頁 |

| 文件大?。?/td> | 1672K |

| 代理商: | AD9865BCPRL |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

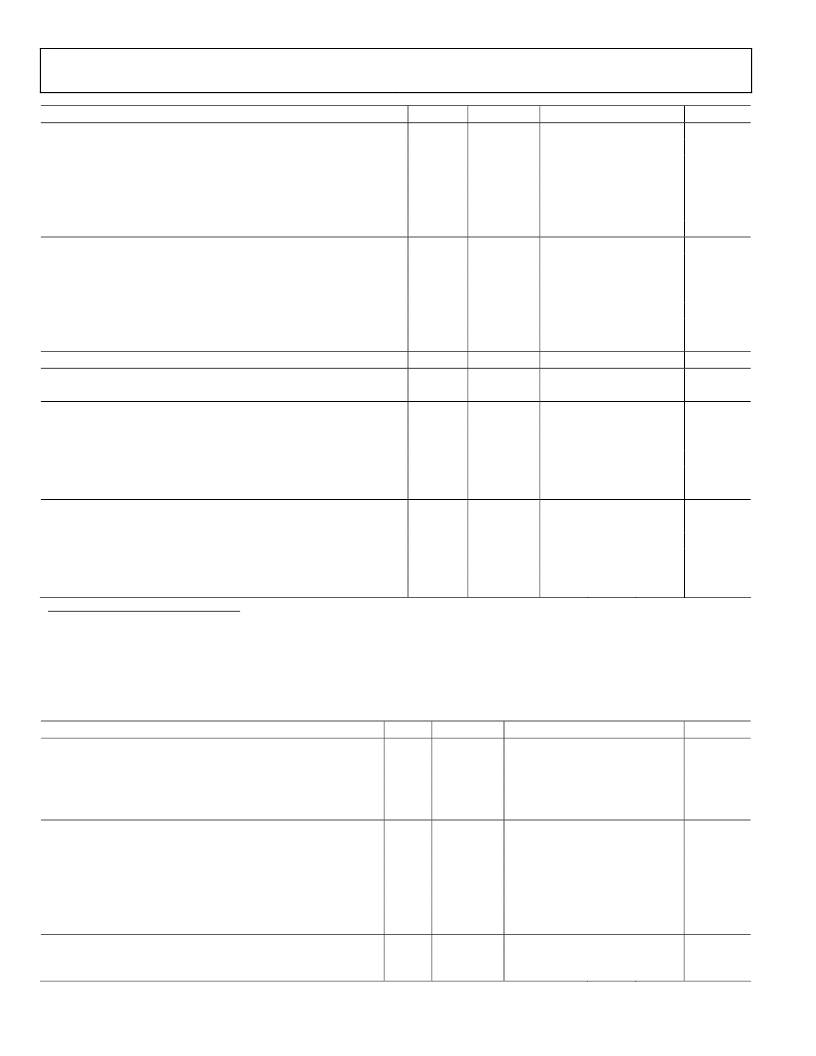

AD9865

Parameter

POWER CONSUMPTION (Half-Duplex Operation with f

DATA

= 50 MSPS)

2

Tx Mode

I

AVDD

+ I

CLKVDD

I

DVDD

+ I

DRVDD

Rx Mode

I

AVDD

+ I

CLKVDD

I

DVDD

+ I

DRVDD

POWER CONSUMPTION OF FUNCTIONAL BLOCKS

1

(I

AVDD

+ I

CLKVDD

)

RxPGA and LPF

ADC

TxDAC

IAMP (Programmable)

Reference

CLK PLL and Synthesizer

MAXIMUM ALLOWABLE POWER DISSIPATION

STANDBY POWER CONSUMPTION

IS_TOTAL (Total Supply Current)

POWER DOWN DELAY (USING PWR_DWN PIN)

RxPGA and LPF

ADC

TxDAC

IAMP

CLK PLL and synthesizer

POWER UP DELAY (USING PWR_DWN PIN)

RxPGA and LPF

ADC

TxDAC

IAMP

CLK PLL and Synthesizer

Rev. A | Page 6 of 48

Temp

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

Full

Full

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

Test Level

IV

IV

IV

IV

III

III

III

III

III

III

IV

III

III

III

III

III

III

III

III

III

III

Min

10

Typ

112

46

225

36.5

87

108

38

170

107

13

440

12

20

20

27

7.8

88

13

20

20

Max

130

49.5

253

39

120

1.66

Unit

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

W

mA

ns

ns

ns

ns

ns

μs

ns

μs

ns

μs

1

Default power-up settings for MODE = HIGH and CONFIG = LOW, IOUTP_FS = 20 mA, does not include IAMP’s current consumption, which is application dependent.

2

Default power-up settings for MODE = LOW and CONFIG = LOW.

DIGITAL SPECIFICATIONS

AVDD = 3.3 V ± 5%, DVDD = CLKVDD = DRVDD = 3.3 V ± 10%; R

SET

= 2 k, unless otherwise noted.

Table 4.

Parameter

Temp

CMOS LOGIC INPUTS

High Level Input Voltage

Full

Low Level Input Voltage

Full

Input Leakage Current

Input Capacitance

Full

CMOS LOGIC OUTPUTS (C

LOAD

= 5 pF)

High Level Output Voltage (I

OH

= 1 mA)

Full

Low Level Output Voltage (I

OH

= 1 mA)

Full

Output Rise/Fall Time (High Strength Mode and C

LOAD

= 15 pF)

Full

Output Rise/Fall Time (Low Strength Mode and C

LOAD

= 15 pF)

Full

Output Rise/Fall Time (High Strength Mode and C

LOAD

= 5 pF)

Full

Output Rise/Fall Time (Low Strength Mode and C

LOAD

= 5 pF)

Full

RESET

Minimum Low Pulse Width (Relative to f

ADC

)

Test Level

VI

VI

VI

VI

VI

VI

VI

VI

VI

Min

DRVDD – 0.7

DRVDD – 0.7

1

Typ

3

1.5/2.3

1.9/2.7

0.7/0.7

1.0/1.0

Max

0.4

12

0.4

Unit

V

V

μA

pF

V

V

ns

ns

ns

ns

Clock

cycles

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9865BCPZ1 | Broadband Modem Mixed-Signal Front End |

| AD9865BCPZRL1 | Broadband Modem Mixed-Signal Front End |

| AD9865CHIPS | Broadband Modem Mixed-Signal Front End |

| AD9887 | Dual Interface for Flat Panel Displays |

| AD9888 | 100/140/170/205 MSPS Analog Flat Panel Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9865BCPZ | 功能描述:IC PROCESSOR FRONT END 64LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點(diǎn):- 封裝/外殼:48-TQFP 裸露焊盤 供應(yīng)商設(shè)備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9865BCPZ1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9865BCPZRL | 功能描述:IC PROCESSOR FRONT END 64LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點(diǎn):- 封裝/外殼:48-TQFP 裸露焊盤 供應(yīng)商設(shè)備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9865BCPZRL1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9865CHIPS | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。