- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375249 > AD9865BCPRL (ANALOG DEVICES INC) Broadband Modem Mixed-Signal Front End PDF資料下載

參數(shù)資料

| 型號(hào): | AD9865BCPRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Broadband Modem Mixed-Signal Front End |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, QCC64 |

| 封裝: | MO-220-VMMD, LFCSP-64 |

| 文件頁(yè)數(shù): | 27/48頁(yè) |

| 文件大小: | 1672K |

| 代理商: | AD9865BCPRL |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

AD9865

TXPGA CONTROL

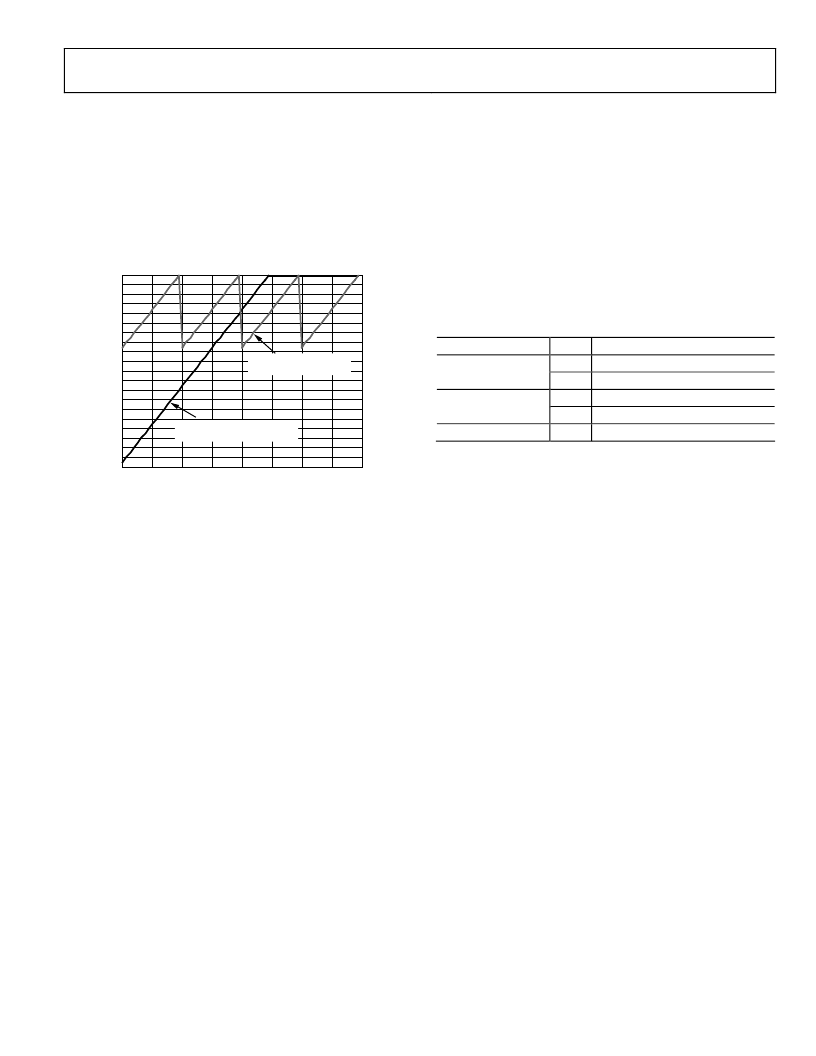

The AD9865 also contains a digital PGA in the Tx path distri-

buted between the TxDAC and IAMP. The TxPGA is used to

control the peak current from the TxDAC and IAMP over a

7.5 dB and 19.5 dB span, respectively, with 0.5 dB resolution.

A 6-bit word is used to set the TxPGA attenuation according to

the mapping shown in Figure 58. The TxDAC gain mapping is

applicable only when Bit 0 of Register 0x0E is set, and only the

four LSBs of the 6-bit gain word are relevant.

Rev. A | Page 27 of 48

0

6-BIT DIGITAL CODE (Decimal Equivalent)

T

0

8

16

24

32

40

48

56

64

0

–20

–16

–17

–18

–19

–14

–15

–12

–13

–10

–11

–8

–9

–6

–7

–2

–3

–4

–5

–1

TxDACs IOUTP OUTPUT

HAS 7.5dB RANGE

IAMPs IOUTN AND IOUTG

OUTPUTS HAS 19.5dB RANGE

Figure 58. Digital Gain Mapping of TxPGA

The TxPGA register can be updated via the PGA[5:0] port or

SPI port. The first method should be considered for fast updates

of the TxPGA register. Its operation is similar to the description

in the RxPGA Control section. The SPI port allows direct up-

date and readback of the TxPGA register via Register 0x0A with

an update rate limited to 1.6 MSPS (SCLK = 32 MHz). Bit 6 of

Register 0x0A must be set for a read or write operation.

Table 17 lists the SPI registers pertaining to the TxPGA. The

TxPGA control register default setting is for minimum

attenuation (0 dBFS) with the PGA[5:0] port disabled for Tx

gain control.

Table 17. SPI Registers TxPGA Control

Address (Hex)

Bit

0x0A

(6)

(5:0)

0x0B

(6)

(5)

0x0E

(0)

Description

Enable TxPGA update via SPI

TxPGA gain code

Select TxPGA via PGA[5:0]

Select RxPGA via PGA[5:0]

TxDAC output (IAMP disabled)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9865BCPZ1 | Broadband Modem Mixed-Signal Front End |

| AD9865BCPZRL1 | Broadband Modem Mixed-Signal Front End |

| AD9865CHIPS | Broadband Modem Mixed-Signal Front End |

| AD9887 | Dual Interface for Flat Panel Displays |

| AD9888 | 100/140/170/205 MSPS Analog Flat Panel Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9865BCPZ | 功能描述:IC PROCESSOR FRONT END 64LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點(diǎn):- 封裝/外殼:48-TQFP 裸露焊盤 供應(yīng)商設(shè)備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9865BCPZ1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9865BCPZRL | 功能描述:IC PROCESSOR FRONT END 64LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點(diǎn):- 封裝/外殼:48-TQFP 裸露焊盤 供應(yīng)商設(shè)備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9865BCPZRL1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9865CHIPS | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。