- 您現(xiàn)在的位置:買賣IC網 > PDF目錄25570 > 9LPRS462AGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 240 MHz, OTHER CLOCK GENERATOR, PDSO8 PDF資料下載

參數(shù)資料

| 型號: | 9LPRS462AGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產生/分配 |

| 英文描述: | 240 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-8 |

| 文件頁數(shù): | 7/23頁 |

| 文件大小: | 248K |

| 代理商: | 9LPRS462AGLFT |

ICS9LPRS462

Low Power Clock for ATI RS/RD600 series chipsets for AMD CPUs

IDTTM/ICSTM

Low Power Clock for ATI RS/RD600 series chipsets for AMD CPUs

1378A—04/07/08

15

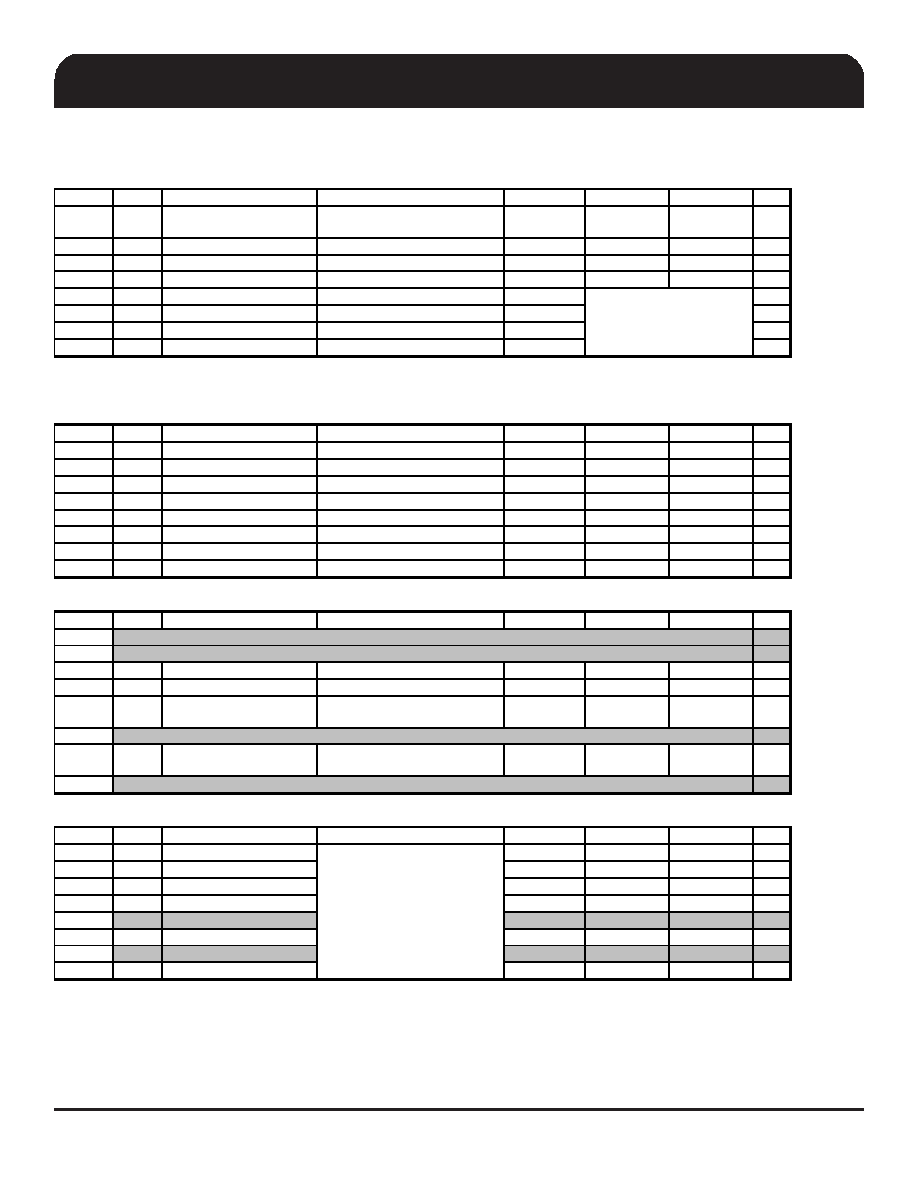

SMBus Table: Spread Spectrum Enable and CPU Frequency Select Register

Byte 0

Pin #

Name

Control Function

Type

0

1

PWD

Bit 7

-

FS Source

Latched Input or SMBus

Frequency Select

RW

Latched

Inputs

SMBus

0

Bit 6

-

ATIG SS_EN

ATIG Spread Spectrum Enable

RW

Disable

Enable

0

Bit 5

-

SRC SS_EN

SRC Spread Spectrum Enable

RW

Disable

Enable

0

Bit 4

-

CPU SS_EN

CPU Spread Spectrum Enable

RW

Disable

Enable

0

Bit 3

-

CPU FS3

CPU Freq Select Bit 3

RW

0

Bit 2

-

CPU FS2

CPU Freq Select Bit 2

RW

Latch

Bit 1

-

CPU FS1

CPU Freq Select Bit 1

RW

Latch

Bit 0

-

CPU FS0

CPU Freq Select Bit 0

RW

Latch

Note: Each Spread Spectrum Enable bit is independent from the other.

Bit(6:4) must all set to "1" in order to enable spread for CPU, SRC and ATIG clocks.

SMBus Table: Output Control Register

Byte 1

Pin #

Name

Control Function

Type

0

1

PWD

Bit 7

7

48MHz_1

48MHz_1 Output Enable

RW

Disable

Enable

1

Bit 6

6

48MHz_0

48MHz_0 Output Enable

RW

Disable

Enable

1

Bit 5

54

REF2

REF2 Output Enable

RW

Disable

Enable

1

Bit 4

55

REF1

REF1 Output Enable

RW

Disable

Enable

1

Bit 3

56

REF0

REF0 Output Enable

RW

Disable

Enable

1

Bit 2

51

HTTCLK0

HTTCLK0 Output Enable

RW

Disable

Enable

1

Bit 1

44,43

CPUCLK1

CPUCLK1 Output Enable

RW

Disable

Enable

1

Bit 0

48,47

CPUCLK0

CPUCLK0 Output Enable

RW

Disable

Enable

1

SMBus Table: ATIGCLK and CLKREQB# Output Control Register

Byte 2

Pin #

Name

Control Function

Type

0

1

PWD

Bit 7

0

Bit 6

0

Bit 5

31,30

ATIGCLK1

ATIGCLK1 Output Enable

RW

Disable

Enable

1

Bit 4

35,34

ATIGCLK0

ATIGCLK0 Output Enable

RW

Disable

Enable

1

Bit 3

20,21

REQBSRC2

CLKREQB# Controls SRC2

RW

Does not

control

Controls

0

Bit 2

0

Bit 1

24,25

REQBSRC1

CLKREQB# Controls SRC1

RW

Does not

control

Controls

0

Bit 0

0

SMBus Table: SRCCLK Output Control Register

Byte 3

Pin #

Name

Control Function

Type

0

1

PWD

Bit 7

12,13

SRCCLK5

RW

Disable

Enable

1

Bit 6

16,17

SRCCLK4

RW

Disable

Enable

1

Bit 5

18,19

SRCCLK3

RW

Disable

Enable

1

Bit 4

20,21

SRCCLK2

RW

Disable

Enable

1

Bit 3

Reserved

-

1

Bit 2

24,25

SRCCLK1

RW

Disable

Enable

1

Bit 1

Reserved

-

1

Bit 0

39,38

SRCCLK0

RW

Disable

Enable

1

See Table 1:

CPU Frequency Selection

Table

Master Output control. Enables

or disables output, regardless of

CLKREQ# inputs.

Reserved

相關PDF資料 |

PDF描述 |

|---|---|

| 9LPRS480YKLFT | PROC SPECIFIC CLOCK GENERATOR, PQCC64 |

| 9LPRS501SKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 |

| 9LPRS501YKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 |

| 9LPRS502YFLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 |

| 9LPRS502YGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 9LPRS464AGLF | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPRS464AGLFT | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPRS471CKLF | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPRS471CKLFT | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPRS476HKLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS476HKLF GENERAL PURPOSE SEMICONDUCTORS - Trays 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS476HKLF General Purpose Semiconductors |

發(fā)布緊急采購,3分鐘左右您將得到回復。