- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4265 > XC3S1400AN-5FGG484C (Xilinx Inc)IC FPGA SPARTAN-3AN 484FPGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC3S1400AN-5FGG484C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 109/123頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3AN 484FPGA |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-3AN |

| LAB/CLB數(shù): | 2816 |

| 邏輯元件/單元數(shù): | 25344 |

| RAM 位總計(jì): | 589824 |

| 輸入/輸出數(shù): | 372 |

| 門數(shù): | 1400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 484-BBGA |

| 供應(yīng)商設(shè)備封裝: | 484-FBGA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)當(dāng)前第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)

Spartan-3AN FPGA Family: Pinout Descriptions

DS557 (v4.1) April 1, 2011

Product Specification

86

User I/Os by Bank

Table 71 and Table 72 indicate how the available user-I/O pins are distributed between the four I/O banks on the FTG256

package. The AWAKE pin is counted as a dual-purpose I/O. The XC3S50AN FPGA in the FTG256 package has 51

unconnected balls, labeled with an N.C. type. These pins are also indicated in Figure 20.

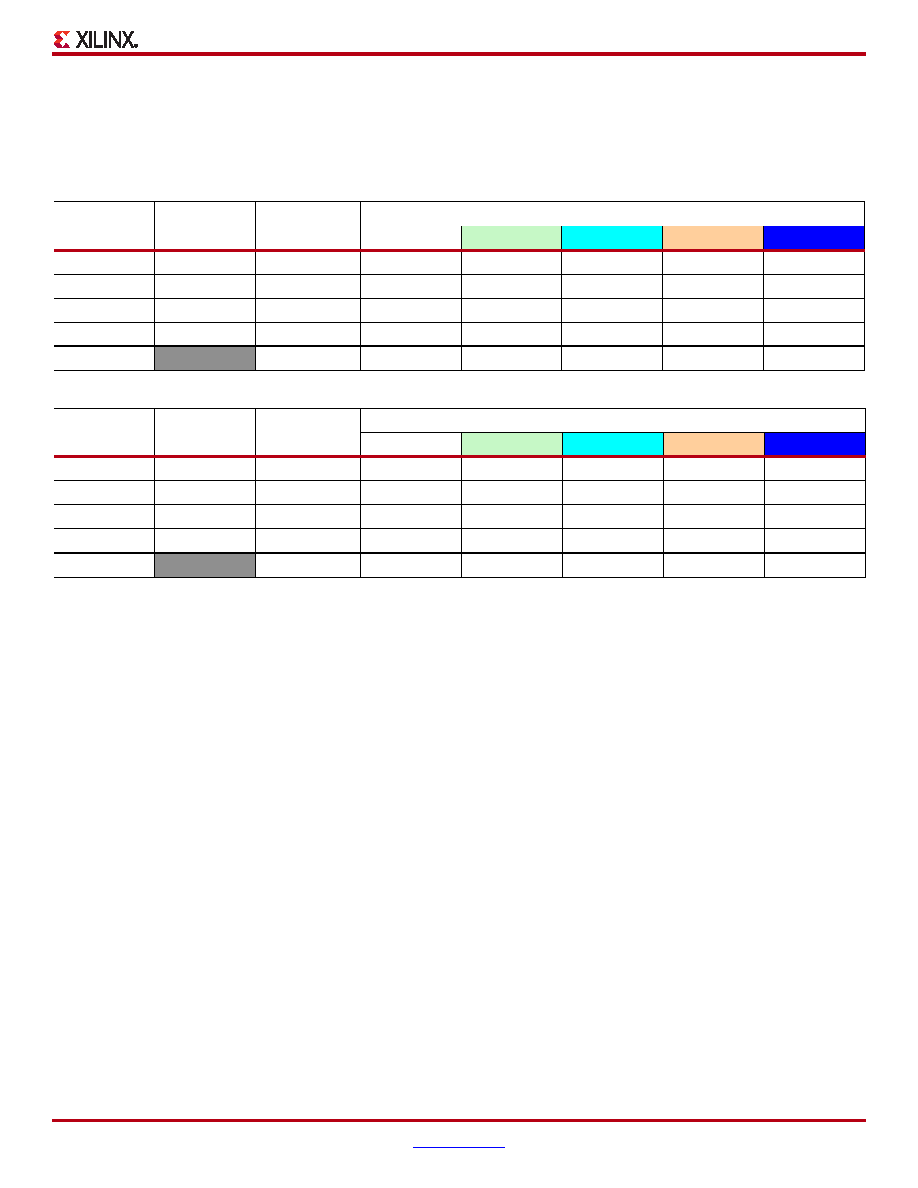

Table 71: User I/Os Per Bank on XC3S50AN in the FTG256 Package

Package

Edge

I/O Bank

Maximum I/Os

All Possible I/O Pins by Type

I/O

INPUT

DUAL

VREF

CLK

Top

0

40

21

7

1

3

8

Right

1

32

12

5

4

3

8

Bottom

2

40

5

2

21

6

Left

3

32

15

6

0

3

8

Total

144

53

20

26

15

30

Table 72: User I/Os Per Bank on XC3S200AN and XC3S400AN in the FTG256 Package

Package

Edge

I/O Bank

Maximum I/Os

All Possible I/O Pins by Type

I/O

INPUT

DUAL

VREF

CLK

Top

0

47

27

6

1

5

8

Right

1

50

1

6

30

5

8

Bottom

2

48

11

2

21

6

8

Left

3

50

30

7

0

5

8

Total

195

69

21

52

21

32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 25AA080DT-I/MNY | IC SRL EEPROM 1KX8 1.8V 8-TDFN |

| 3344-38 | SCREW BRDLOCK M2.5 0.31" 1=1PC |

| XCV50E-7PQ240C | IC FPGA 1.8V 71K GATES 240-PQFP |

| 25AA080CT-I/MNY | IC SRL EEPROM 1KX8 1.8V 8-TDFN |

| 3344-26 | SCREW BRDLOCK M2.6 0.31" 1=1PC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S1400AN-5FGG676C | 功能描述:IC FPGA SPARTAN -3N1400K 676FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3AN 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計(jì):221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| XC3S1500 | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1500-4CP132C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1500-4CP132I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1500-4CPG132C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA Family: Complete Data Sheet |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。