- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359439 > VT82C586A (Electronic Theatre Controls, Inc.) PIC Integrated Peripheral Controller PDF資料下載

參數(shù)資料

| 型號(hào): | VT82C586A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | PIC Integrated Peripheral Controller |

| 中文描述: | 石化整合的周邊控制器 |

| 文件頁(yè)數(shù): | 18/43頁(yè) |

| 文件大?。?/td> | 215K |

| 代理商: | VT82C586A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)

9,$7HFKQRORJLHV,QF

VT82C586A

Preliminary Revision 0.1

October 13, 1996

-

12-

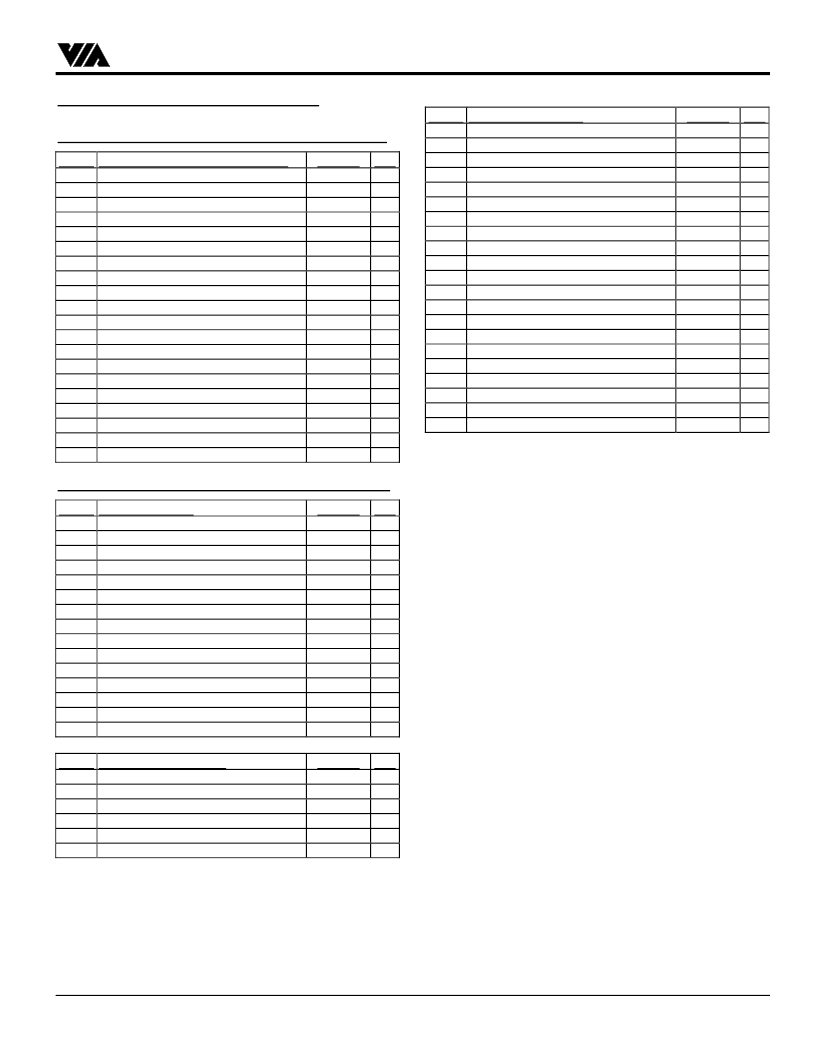

Register Overview

PCI Function 0 Registers - PCI-to-ISA Bridge

Configuration Space PCI-to-ISA Bridge Header Registers

Offset PCI Configuration Space Header

1-0

Vendor ID

3-2

Device ID

5-4

Command

7-6

Status

8

Revision ID

9

Programming Interface

A

Sub Class Code

B

Base Class Code

C

-reserved- (cache line size)

D

-reserved- (latency timer)

E

Header Type

F

Built In Self Test (BIST)

10-27 -reserved- (base address registers)

28-2F -reserved- (unassigned)

30-33 -reserved- (expansion ROM base

34-3B -reserved- (unassigned)

3C

-reserved- (interrupt line)

3D

-reserved- (interrupt pin)

3E

-reserved- (min gnt)

3F

-reserved- (max lat)

Default

1106

0586

000F

0200

nn

00

01

06

00

00

80

00

00

00

00

00

00

00

00

00

Acc

RO

RO

RW

WC

RO

RO

RO

RO

—

—

RO

RO

—

—

—

—

—

—

—

—

Configuration Space PCI-to-ISA Bridge-Specific Registers

Offset ISA Bus Control

40

ISA Bus Control

41

Refresh and Port 92

42

ISA Clock Control

43

ROM Decode Control

44

Keyboard Controller Control

45

Type F DMA Control

46

Miscellaneous Control 1

47

Miscellaneous Control 2

48

Miscellaneous Control 3

49

-reserved-

4A

IDE Interrupt Routing

4B

-reserved-

4C

DMA / Master Mem Access Control 1

4D

DMA / Master Mem Access Control 2

4F-4E DMA / Master Mem Access Control 3

Default

00

00

00

00

00

00

00

00

01

00

04

00

00

00

0300

Acc

RW

RW

RW

RW

RW

RW

RW

RW

RW

—

RW

—

RW

RW

RW

Offset Plug and Play Control

50

PNP DRQ Routing

51-53 -reserved-

54

PCI IRQ Edge / Level Selection

55

PNP IRQ Routing 1

56

PNP IRQ Routing 2

57

PNP IRQ Routing 3

Default

24

00

00

00

00

00

Acc

RW

—

RW

RW

RW

RW

Offset Power Management

80

Primary Activity Detect Enable

81

-reserved-

82

Primary Activity Detect Status

83

-reserved-

85-84 SMI Event Enable

87-86 SMI Status

88

Timer Control 1

89

Timer Control 2

8A

Timer Control 3

8B

GP Timer Reload Enable

8C

Conserve Mode / Secondary Event

8D

Miscellaneous Control

8E

STPCLK# Duty Cycle

90

ISA Interrupt 7-0 as Primary Event

91

ISA Interrupt 15-8 as Primary Event

92

ISA Interrupt 7-0 as Secondary Event

93

ISA Interrupt 15-8 as Secondary

94

External SMI Pin Status

95

Power-Up Strap Option 1

96

Power-Up Strap Option 2

97-FF -reserved-

Power-up default value depends on external strapping

Default

00

00

00

00

0000

0000

00

00

00

00

00

00

00

00

00

00

00

00

00

Acc

RW

—

WC

—

RW

WC

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RO

RO

RO

—

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VT82C586B | PCI INTEGRATED PERIPHERAL CONTROLLER |

| VT82C686A | PCI SUPER-I/O INTEGRATED PERIPHERAL CONTROLLER |

| vt82c693 | APOLLO PRO-PLUS |

| VT8371 | KX133 ATHLON NORTH BRIDGE |

| VT83A333 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VT82C586B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:PCI INTEGRATED PERIPHERAL CONTROLLER |

| VT82C596 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MOBILE PCI INTEGRATED PERIPHERAL CONTROLLER |

| VT82C596A | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MOBILE PCI INTEGRATED PERIPHERAL CONTROLLER |

| VT82C596B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:PCI INTEGRATED PERIPHERAL CONTROLLER |

| VT82C598MVP | 制造商:Via Technologies Inc 功能描述:SYSTEM CONTROLLER, 476 Pin, BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。