- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359431 > VSC8117QP1 (VITESSE SEMICONDUCTOR CORP) GIGATRUE 550 CAT6 PATCH 25 FT, SNAGLESS, BLUE PDF資料下載

參數(shù)資料

| 型號: | VSC8117QP1 |

| 廠商: | VITESSE SEMICONDUCTOR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | GIGATRUE 550 CAT6 PATCH 25 FT, SNAGLESS, BLUE |

| 中文描述: | TRANSCEIVER, PQFP64 |

| 封裝: | 10 X 10 MM, HEAT SPREADER, PLASTIC, QFP-64 |

| 文件頁數(shù): | 6/22頁 |

| 文件大?。?/td> | 406K |

| 代理商: | VSC8117QP1 |

VITESSE

Data Sheet

VSC8117

ATM/SONET/SDH 622/155 Mb/s Transceiver Mux/Demux

with Integrated Clock Generation and Clock Recovery

Page 6

VITESSE

SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 805/388-3700 FAX: 805/987-5896

G52221-0, Rev 4.1

1/8/00

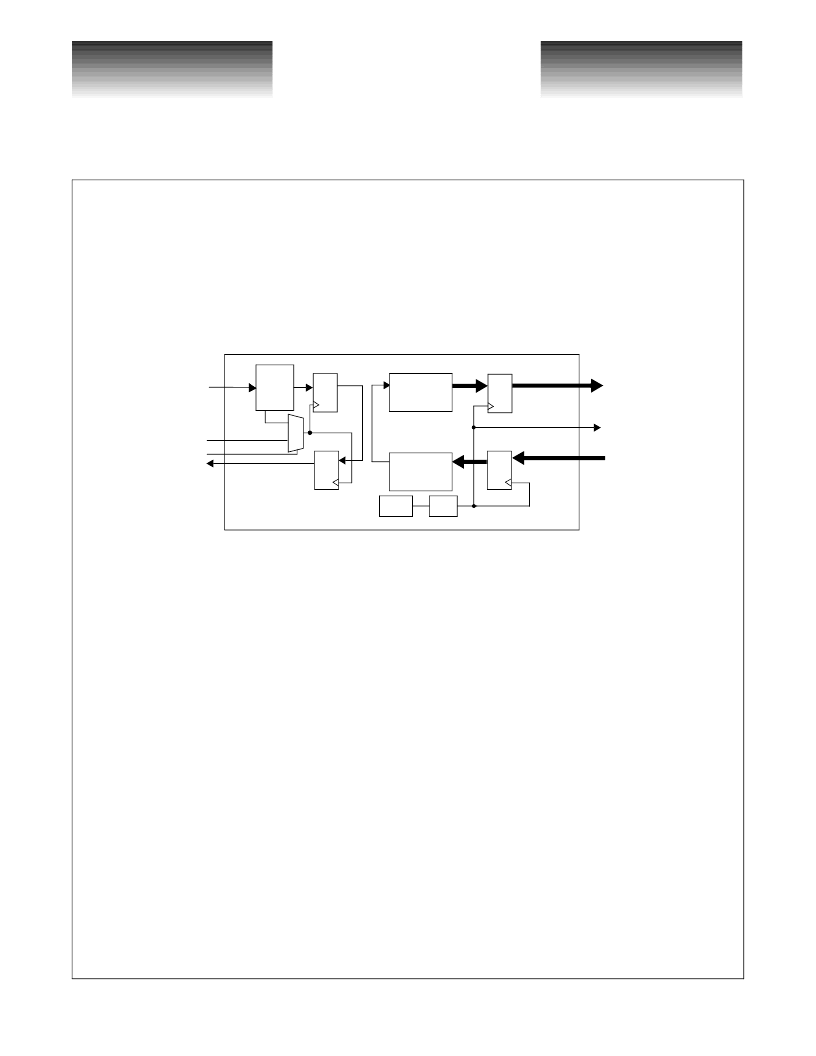

Split Loopback

Equipment and facility loopback modes can be enabled simultaneously. In this case, high-speed serial data

received (RXDATAIN) is mux’d through to the high-speed serial output (TXDATAOUT). The low-speed trans-

mit byte wide bus(TXIN[7:0]) and (TXLSCKIN) are mux’d into the low-speed byte wide receive output bus

(RXOUT[7:0]) and (RXLSCKOUT). See Figure 5.

Figure 5: Split Loopback Datapath

Loop Timing

LOOPTIM0 mode bypasses the CMU when the LOOPTIM0 input is asserted high. In this mode the CMU

is bypassed by using the receive clock (RXCLKIN), and the entire part is synchronously clocked from a single

external source.

Clock Synthesis

The VSC8117 uses an integrated phase-locked loop (PLL) for clock synthesis of the 622MHz high speed

clock used for serialization in the transmitter section. The PLL is comprised of a phase-frequency detector

(PFD), an integrating operation amplifier and a voltage controlled oscillator (VCO) configured in classic feed-

back system. The PFD compares the selected divided down version of the 622MHz VCO (pin CMUFREQSEL

selects the divide-by ratios of 8 or 32, see Table 10) and the reference clock. The integrator provides a transfer

function between input phase error and output voltage control. The VCO portion of the PLL is a voltage con-

trolled ring-oscillator with a center frequency of 622MHz.

The reactive elements of the integrator are located off-chip and are connected to the feedback loop of the

amplifier through the CP1, CP2, CN1 and CN2 pins. The configuration of these external surface mounted

capacitors is shown in Figure 6. Table 1 shows the recommended external capacitor values for the configurable

reference frequencies.

D

Q

D

Q

S1:8

Parallel

Q

D

RXDATAIN

TXDATAOUT

RXOUT[7:0]

Q

D

P8:1

Serial

TXIN[7:0]

0

1

CRU

RXCLKIN

DSBLCRU

RXLSCKOUT

RClock

÷

8

PLL

TXLSCKIN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VSC8117QP2 | GIGATRUE 550 CAT6 PATCH 30 FT. SNAGLESS BLUE |

| VSC8121QI | 2.488GHz SONET/SDH Clock Generator |

| VSC8121 | 2.488GHz SONET/SDH Clock Generator |

| VSC8122 | Multi-Rate SONET/SDH Clock and Data Recovery IC |

| VSC8122QP | Multi-Rate SONET/SDH Clock and Data Recovery IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VSC8117QP2 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:ATM/SONET/SDH 622/155 Mb/s Transceiver Mux/Demux with Integrated Clock Generation and Clock Recovery |

| VSC8121 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:2.488GHz SONET/SDH Clock Generator |

| VSC8121QI | 制造商:Vitesse Semiconductor Corporation 功能描述: |

| VSC8122 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:Multi-Rate SONET/SDH Clock and Data Recovery IC |

| VSC8122QP | 制造商:Vitesse Semiconductor Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。