- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383982 > UPD6708GS (NEC Corp.) IEBusa Inter Equipment Busa PROTOCOL CONTROL LSI PDF資料下載

參數(shù)資料

| 型號: | UPD6708GS |

| 廠商: | NEC Corp. |

| 英文描述: | IEBusa Inter Equipment Busa PROTOCOL CONTROL LSI |

| 中文描述: | IEBusa設(shè)備布薩間協(xié)議控制大規(guī)模集成電路 |

| 文件頁數(shù): | 47/72頁 |

| 文件大小: | 292K |

| 代理商: | UPD6708GS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當(dāng)前第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

47

μ

PD6708

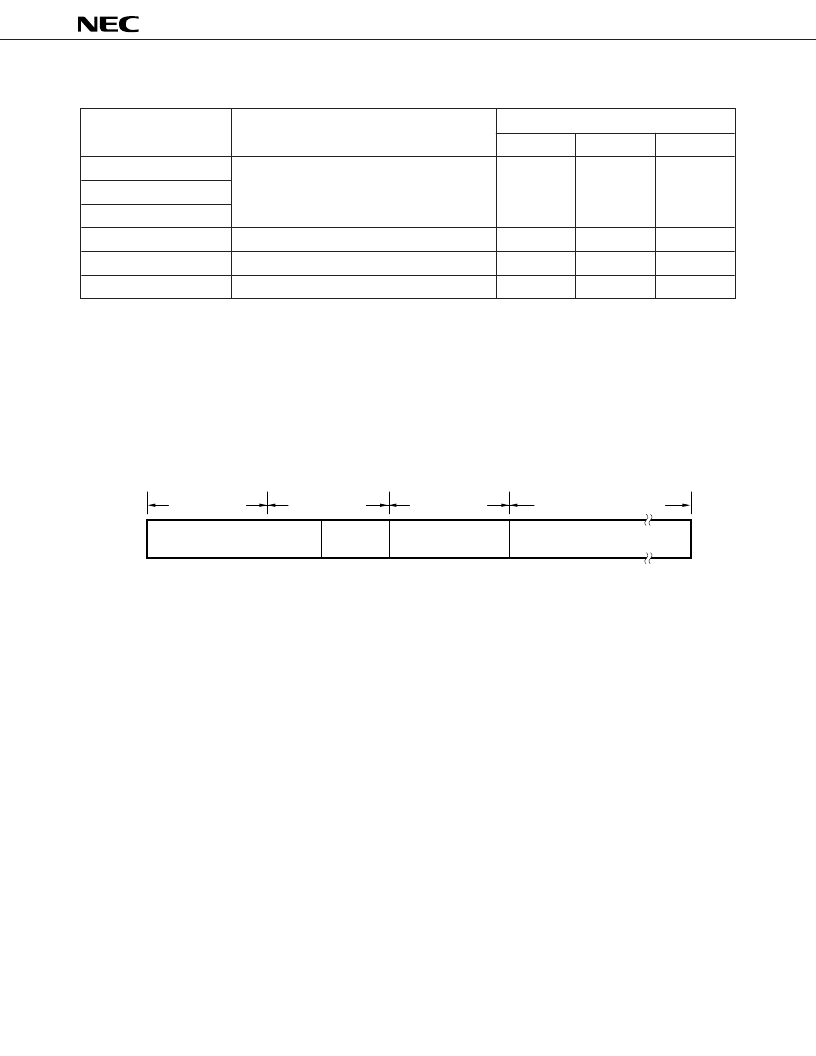

Table 7-4. Placing Receive Data in RDB

Parameter/

Communication Data

Areas where RDB is read

Time (

μ

s)

Note

Mode 0

Mode 1

Mode 2

Master address

When ACK bit is received in message length field

0

0

0

Control bits

Message length bits

Receive data (first byte)

When first ACK bit is received in data field

Approx. 1580

Approx. 400

Approx. 290

Receive data (second byte)

When second ACK bit is received in data field

Approx. 3160

Approx. 800

Approx. 580

Receive data (N-th byte)

When N-th ACK bit is received in data field

Approx. 1580

×

N

Approx. 400

×

N

Approx. 290

×

N

Note

Minimum time after the “slave reception start” return code is placed in STR and an interrupt request is generated.

7.5

Broadcast Reception

(1)

When a broadcast reception unit receives the message length field, the master address, control bits and message

length bits are placed in RDB as shown in Figure 7-6, a “broadcast reception start” return code (CH) is placed in STR,

and an interrupt request is generated.

Figure 7-6. Data Exchange During Broadcast Reception (Contents of RDB)

(2)

(3)

Each time one byte of receive data is received, it is placed in RDB.

Each time 20 bytes (RDB capacity) of receive data are received, if RDB is full, a “slave receive buffer full” return code

(DH) is placed in STR, and an interrupt request is generated.

After the final data of one frame is placed in RDB, a “broadcast reception normal termination” return code (EH) is placed

in STR and an interrupt request is generated.

If a communication error occurs during reception and communication stops without receiving all of the data transmitted

from the master unit, a “termination during broadcast reception” return code (FH) is placed in STR and an interrupt request

is generated.

(4)

(5)

The areas where the

μ

PD6708 places receive data, etc., in RDB are the same as those shown in Table 7-4.

Master Address (12 Bits)

First Byte

Second Byte

Third Byte

Fourth Byte Onward

RDB

Message Length Bits

Control Bits

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD6951 | 6 BIT D/A CONVERTER FOR VIDEO SIGNAL PROCESSING CMOS LSI |

| UPD6951C | 6 BIT D/A CONVERTER FOR VIDEO SIGNAL PROCESSING CMOS LSI |

| UPD6951G | 6 BIT D/A CONVERTER FOR VIDEO SIGNAL PROCESSING CMOS LSI |

| UPD703130GC-8EU | MOS INTEGRATED CIRCUIT |

| UPD703130 | MOS INTEGRATED CIRCUIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD6708GS(A) | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD67100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| UPD67101 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| UPD67240 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| UPD67A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontrollers for Remote Controllers Pamphlet | Pamphlet[11/2002] |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。