- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384043 > UPD44324182F5-E37-EQ2-A (NEC Corp.) 36M-BIT DDRII SRAM 2-WORD BURST OPERATION PDF資料下載

參數(shù)資料

| 型號(hào): | UPD44324182F5-E37-EQ2-A |

| 廠商: | NEC Corp. |

| 元件分類: | DRAM |

| 英文描述: | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| 中文描述: | 36M條位SRAM的2條DDRII字爆發(fā)運(yùn)作 |

| 文件頁(yè)數(shù): | 22/40頁(yè) |

| 文件大小: | 361K |

| 代理商: | UPD44324182F5-E37-EQ2-A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

22

Data Sheet M16780EJ3V0DS

μ

PD44324082, 44324092, 44324182, 44324362

JTAG Specification

These products support a limited set of JTAG functions as in IEEE standard 1149.1.

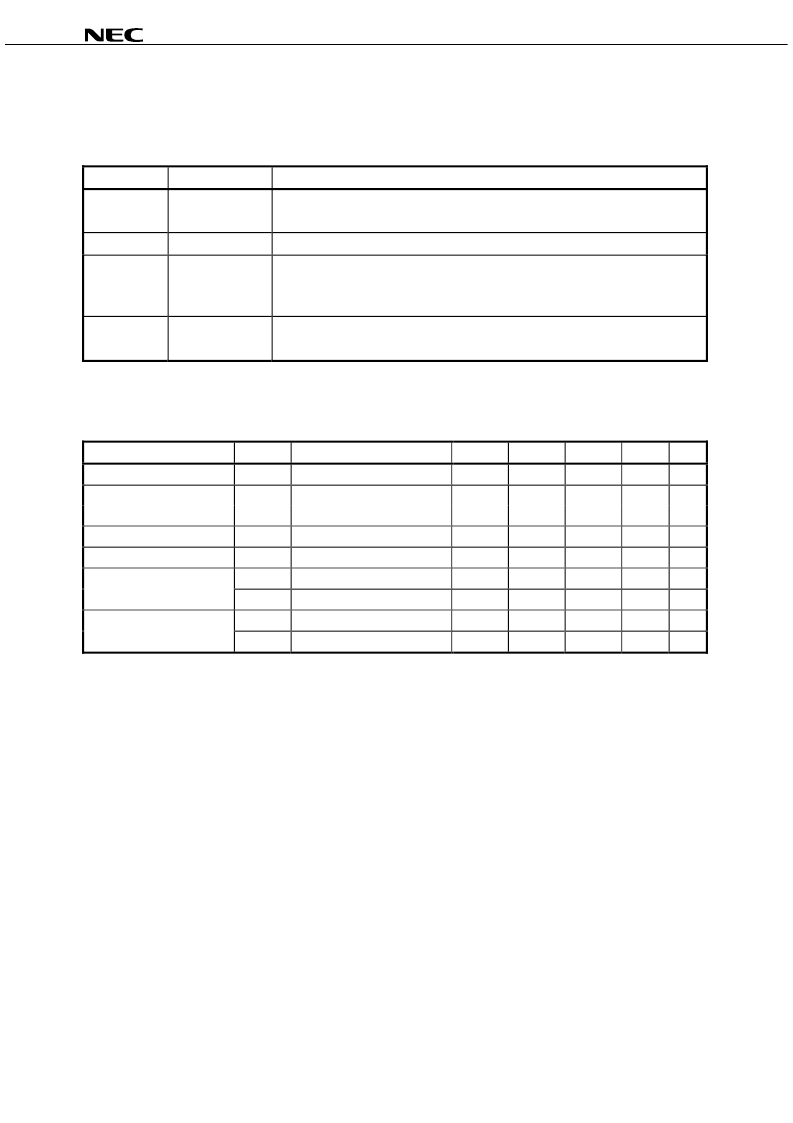

Test Access Port (TAP) Pins

Pin name

Pin assignments

Description

TCK

2R

Test Clock Input. All input are captured on the rising edge of TCK and all outputs

propagate from the falling edge of TCK.

TMS

10R

Test Mode Select. This is the command input for the TAP controller state machine.

TDI

11R

Test Data Input. This is the input side of the serial registers placed between TDI and

TDO. The register placed between TDI and TDO is determined by the state of the TAP

controller state machine and the instruction that is currently loaded in the TAP instruction.

TDO

1R

Test Data Output. This is the output side of the serial registers placed between TDI and

TDO. Output changes in response to the falling edge of TCK.

Remark

The device does not have TRST (TAP reset). The Test-Logic Reset state is entered while TMS is held high

for five rising edges of TCK. The TAP controller state is also reset on the SRAM POWER-UP.

JTAG DC Characteristics (T

A

= 0 to 70°C, V

DD

= 1.8 ± 0.1 V, unless otherwise noted)

Parameter

Symbol

Conditions

MIN.

TYP.

MAX.

Unit

Note

JTAG Input leakage current

I

LI

0 V

≤

V

IN

≤

V

DD

–5.0

–

+5.0

μ

A

JTAG I/O leakage current

I

LO

0 V

≤

V

IN

≤

V

DD

Q,

–5.0

–

+5.0

μ

A

Outputs disabled

JTAG input high voltage

V

IH

1.3

–

V

DD

+0.3

V

JTAG input low voltage

V

IL

–0.3

–

+0.5

V

JTAG output high voltage

V

OH1

| I

OHC

| = 100

μ

A

1.6

–

–

V

V

OH2

| I

OHT

| = 2 mA

1.4

–

–

V

JTAG output low voltage

V

OL1

I

OLC

= 100

μ

A

–

–

0.2

V

V

OL2

I

OLT

= 2 mA

–

–

0.4

V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD44324182F5-E40-EQ2-A | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| UPD44324182F5-E50-EQ2-A | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| UPD44324362F5-E37-EQ2 | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| UPD44324362F5-E37-EQ2-A | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

| UPD44324362F5-E40-EQ2-A | 36M-BIT DDRII SRAM 2-WORD BURST OPERATION |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD44324185BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:SRAM Chip Sync Dual 1.8V 36M-Bit 2M x 18 0.45ns 165-Pin BGA 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324362BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324362BF5-E40-FQ1-A | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324365BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324365BF5-E40-FQ1-A | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。