- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225472 > UPD44165094AF5-E40Y-EQ2 2M X 9 QDR SRAM, 0.45 ns, PBGA165 PDF資料下載

參數(shù)資料

| 型號(hào): | UPD44165094AF5-E40Y-EQ2 |

| 元件分類: | SRAM |

| 英文描述: | 2M X 9 QDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 13 X 15 MM, PLASTIC, BGA-165 |

| 文件頁(yè)數(shù): | 6/40頁(yè) |

| 文件大?。?/td> | 388K |

| 代理商: | UPD44165094AF5-E40Y-EQ2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

14

Data Sheet

M17771EJ3V0DS

μPD44165084A, 44165094A, 44165184A, 44165364A

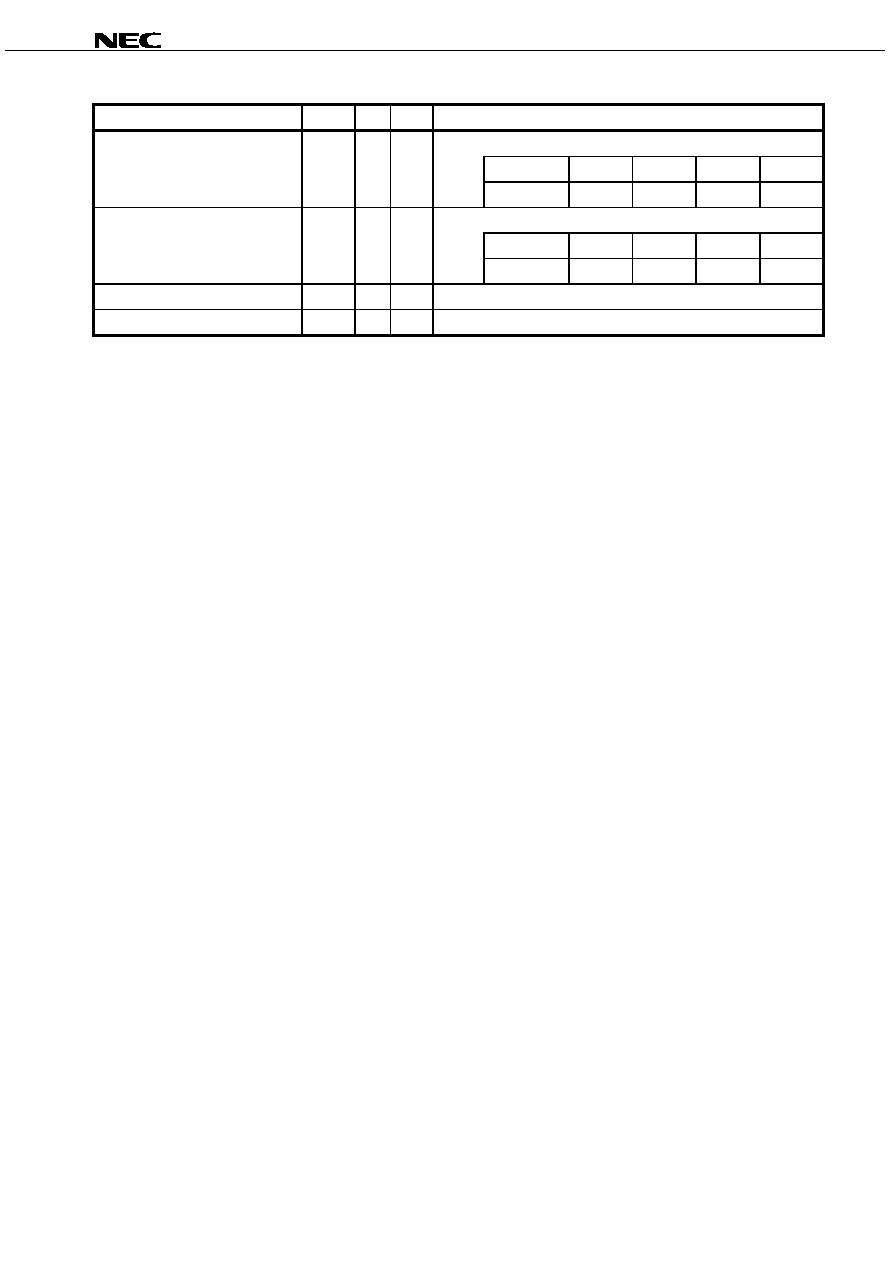

Truth Table

Operation

CLK

R#

W#

D or Q

WRITE cycle

L

→ H

H

L

Data in

Load address, input write data on two

Input data

DA(A+0)

DA(A+1)

DA(A+2)

DA(A+3)

consecutive K and K# rising edge

Input clock

K(t+1)

↑

K#(t+1)

↑

K(t+2)

↑

K#(t+2)

↑

READ cycle

L

→ H

L

X

Data out

Load address, read data on two

Output data

QA(A+0)

QA(A+1)

QA(A+2)

QA(A+3)

consecutive C and C# rising edge

Output clock

C#(t+1)

↑

C(t+2)

↑

C#(t+2)

↑

C(t+3)

↑

NOP (No operation)

L

→ H

H

D = X, Q = High-Z

Clock stop

Stopped

X

Previous state

Remarks 1. H : HIGH, L : LOW,

× : don’t care, ↑ : rising edge.

2. Data inputs are registered at K and K# rising edges. Data outputs are delivered at C and C# rising edges

except if C and C# are HIGH then data outputs are delivered at K and K# rising edges.

3. R# and W# must meet setup/hold times around the rising edge (LOW to HIGH) of K and are registered at

the rising edge of K.

4. This device contains circuitry that ensure the outputs to be in high impedance during power-up.

5. Refer to state diagram and timing diagrams for clarification.

6. It is recommended that K = K# = C = C# when clock is stopped. This is not essential but permits most

rapid restart by overcoming transmission line charging symmetrically.

7. If R# was LOW to initiate the previous cycle, this signal becomes a don't care for this WRITE operation

however it is strongly recommended that this signal is brought HIGH as shown in the truth table.

8. W# during write cycle and R# during read cycle were HIGH on previous K clock rising edge. Initiating

consecutive READ or WRITE operations on consecutive K clock rising edges is not permitted. The

device will ignore the second request.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD44325084F5-E50-EQ2-A | 4M X 8 QDR SRAM, 0.45 ns, PBGA165 |

| UPFS120P | P-CHANNEL, Si, SMALL SIGNAL, MOSFET |

| UPL40-U1BT | CABLE TERMINATED, MALE, TNC CONNECTOR, PLUG |

| UPN2AS | FEMALE-FEMALE-MALE, RF Y ADAPTER |

| UPRLED630 | SINGLE COLOR LED, BRIGHT RED, 1.4732 mm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD44165094BF5-E40-EQ3-A | 制造商:Renesas Electronics Corporation 功能描述:SRAM Chip Sync Dual 1.8V 18M-Bit 2M x 9-Bit 0.45ns 165-Pin BGA |

| UPD44165362BF5-E40-EQ3 | 制造商:Renesas Electronics Corporation 功能描述:UPD44165362BF5-E40-EQ3 - Trays |

| UPD44165362BF5-E40-EQ3-A | 制造商:Renesas Electronics Corporation 功能描述:SRAM Chip Sync Dual 1.8V 18M-Bit 512K x 36 0.45ns 165-Pin BGA |

| UPD44321182GF-A50(A) | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD44324182BF5-E40-FQ1-A | 制造商:Renesas Electronics Corporation 功能描述:RENUPD44324182BF5-E40-FQ1-A 36M-BIT(2M-W |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。