- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98305 > TVP5020CPFP (TEXAS INSTRUMENTS INC) COLOR SIGNAL DECODER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | TVP5020CPFP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL DECODER, PQFP80 |

| 封裝: | POWERPAD, PLASTIC, HTQFP-80 |

| 文件頁數(shù): | 28/87頁 |

| 文件大?。?/td> | 394K |

| 代理商: | TVP5020CPFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁

2–20

2.7.1

VIP Host Port Terminal Description

Table 2–4. VIP Host Port Terminal Description

SIGNAL

TYPE

DESCRIPTION

VC3 (VIPCLK)

I

VIP Host clock (25 MHz – 33 MHz)

VC0 VC1 (HAD[0:1])

I/O

Host address/data bus

VC0 = (HAD_0)

VC1 = (HAD_1)

VC2 (HCTL)

I/O (OD)

Host control: This includes the symbolic signals of VFRAME, DTACK, and VSTOP

INTREQ (VIRQ#)

O (OD)

Interrupt request. Shared signal with VDP

VC3 (VIPCLK) is the host port clock, operating from 25 MHz–33 MHz. VIPCLK can come from any source.

VC0 and VC1 (HAD[0:1]) is a two-wire bus that transfers commands, addresses, and data between master

and slave devices.

VC2 (HCTL) is a shared control terminal. The master drives it to initiate and terminate data transfers. The

slave drives it to terminate and add wait states to data transfers. Because VC2 is a shared control signal,

special attention must be given to its generation to avoid bus conflicts.

INTREQ is a normally open drain pin that signals interrupts to the host controller. Using the interrupt

configuration register at subaddress C2, this terminal can be configured as a conventional CMOS I/O buffer

(non-open drain). Conflict is possible if multiple devices are connected to the INTREQ signal when it is

configured in non-open drain mode.

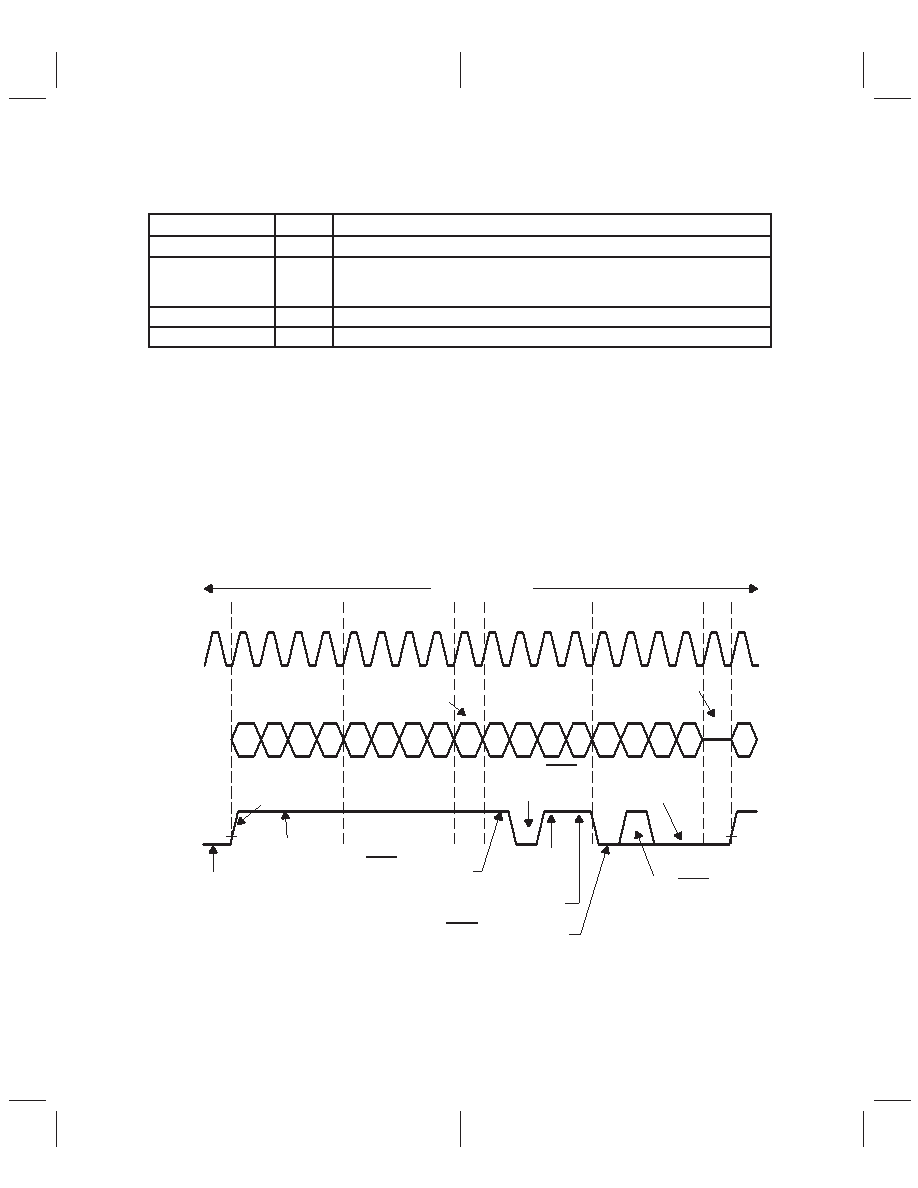

2.7.2

VIP Phases

Command Phase

Address Phase

DC

Retry Phase

Data Phase

TAPh

Command

Address

7:6

5:4

3:2

1:0

7:6

5:4

3:2

1:0

Don’t

Care

Don’t

Care

Don’t

Care

Don’t

Care

Don’t

Care

7:6

5:4

3:2

1:0

7:6

Data

Decode Phase Allows

Slave to Decode

Address

Bus Turn Around Phase

Cmd

Master Drive HCTL High

to Start Transfer

Slave Drives DTACK to

Signal Data is Ready for

the Next Phase

GUI Must Drive This

Low Dring Idle

Master Drives Low

During Idle

Master 3-states

VC2 (HCTL) Floats

VSTOP Can Drive Low to

Terminate The Transfer. If Terminated

There Will Be No Data Phase

Slave Drives High if

Not Terminated in

Cycle

Slave 3-states

VC2 (HCTL) Remains High

FRAME and or VSTOP Drives

Low to Terminate The Transfer

Slave May Drive DTACK Low For

The Next Byte. It is Irrelevant as

Transfer is Already Terminated

VC3

(VIPCLK)

VC0 (HAD0)

VC1 (HAD1)

VC2

(HCTL)

Zero Wait State

Figure 2–21. VIP Transfer Example

相關PDF資料 |

PDF描述 |

|---|---|

| TVP5020 | COLOR SIGNAL DECODER, PQFP80 |

| TVP5022 | COLOR SIGNAL DECODER, PQFP80 |

| TVP5031PFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5040CPFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5040PFP | COLOR SIGNAL DECODER, PQFP80 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TVP5020PFC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| TVP5020TQFP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:NTSC/PAL VIDEO DECODER |

| TVP5021PFP | 功能描述:視頻 IC NTSC/PAL DIGITAL VIDEO DECODER RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TVP5021PFPG4 | 功能描述:視頻 IC NTSC/PAL DIGITAL VIDEO DECODER RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TVP5031 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:NTSC/PAL VIDEO DECODER |

發(fā)布緊急采購,3分鐘左右您將得到回復。