- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384012 > TMC22091KHC (FAIRCHILD SEMICONDUCTOR CORP) Digital Video Encoders/Layering Engine PDF資料下載

參數(shù)資料

| 型號(hào): | TMC22091KHC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | Digital Video Encoders/Layering Engine |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP100 |

| 封裝: | 3.20 MM HEIGHT, MQFP-100 |

| 文件頁數(shù): | 7/60頁 |

| 文件大小: | 293K |

| 代理商: | TMC22091KHC |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

PRODUCT SPECIFICATION

TMC22091/TMC22191

7

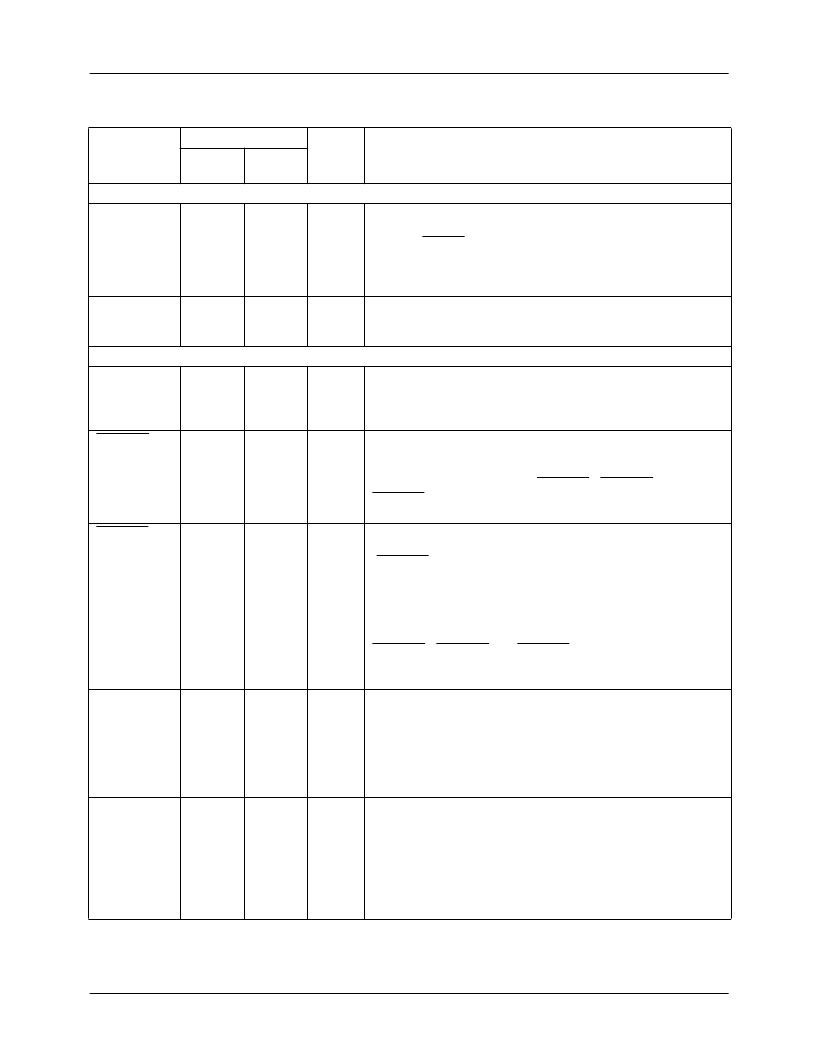

Pin Descriptions

Pin Name

Clocks

PXCK

Pin Number

84-Lead

PLCC

Value

Pin Function Description

100-Lead

MQFP

79

60

TTL

Master Clock Input.

This 20 to 30 MHz clock is internally

divided by 2 to generate the internal pixel clock, PCK, which a

LOW on RESET forces LOW. PXCK drives the entire

TMC22x91, except the asynchronous microprocessor interface

and the semi-synchronous LDV data input clock. All internal

registers are strobed on the rising edge of PXCK.

Pixel Data Load Clock.

On each rising edge of LDV, data on

PD

23-0

are latched into the input preload register, for transfer

into the input demultiplexer on the next rising edge of PCK.

LDV

78

59

TTL

Frame Buffer Interface

PD

23-0

52-63,

66-77

26, 27,

31-40,

43-51,

56-58

80

TTL

Pixel Data Inputs.

In YC

B

C

R

, GBR, RGB, and color-indexed

mode, pixel data enter the TMC22x91 on PD

23-0

. The specific

format is found in Figures 1a and 1b. LDV is the clock that

controls the loading of pixel data.

Horizontal Sync I/O.

In Master and Genlock modes, the

TMC22x91 outputs horizontal sync on this pin. In Slave modes,

the TMC22x91 accepts and locks to horizontal sync input on

this pin (with vertical sync on VVSYNC). VHSYNC and

VVSYNC must be coincident since they are clocked into the

TMC22x91 on the same rising edge of PXCK.

Vertical Sync I/O.

In separate V and H sync Master and

Genlock modes, the TMC22x91 outputs vertical block sync

(VVSYNC LOW for the 2.5 (PAL) or 3 (NTSC) lines on which

vertical sync pulses occur). In composite sync (H and V sync

on same signal) Master and Genlock modes, the TMC22x91

outputs horizontal sync, vertical sync, and equalization over

this pin. In Slave mode, the TMC22x91 accepts and locks to

vertical sync input on this pin (with horizontal sync on

VHSYNC). VHSYNC and VVSYNC must be coincident such

that they are clocked into the TMC22x91 on the same rising

edge of PXCK.

Pixel Data Control.

In Master mode, the TMC22x91 forces

PDC HIGH when and only when it wants active video from the

frame buffer. During blanking (syncs, equalization, burst, and

porches), it forces PDC LOW, signaling that it will ignore any

data presented over PD

23-0

. When PDC is used as an input,

forcing it HIGH allows the TMC22x91 to receive PD during the

active video state.

Hardware Key Input.

When the HKEN control bit is set HIGH

and hardware key pin, KEY, is HIGH, video data entering on

CVBS

7-0

are routed to the COMPOSITE output. This control

signal is pipelined so the pixel that is presented to the PD port

when the KEY signal is invoked is at the midpoint of the soft

key transition. When HKEN is LOW, KEY is ignored. Like PD

data, KEY is clocked into the TMC22x91 on the rising edge of

LDV.

VHSYNC

12

TTL

VVSYNC

13

81

TTL

PDC

11

77

TTL

KEY

4

70

TTL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC22191KHC | Digital Video Encoders/Layering Engine |

| TMC22091R0C | Digital Video Encoders/Layering Engine |

| TMC22191R0C | Digital Video Encoders/Layering Engine |

| TMC22091 | Digital Video Encoders(數(shù)字視頻編碼器) |

| TMC22191 | Digital Video Encoders(數(shù)字視頻編碼器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC22091R0C | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC22091R0CT | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC22091ROC-T | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC22151AKHC | 制造商:CADEKA 制造商全稱:CADEKA 功能描述:Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22151KHC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。