- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383837 > ST16C654IJ68 (EXAR CORP) 2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO PDF資料下載

參數(shù)資料

| 型號: | ST16C654IJ68 |

| 廠商: | EXAR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO |

| 中文描述: | 4 CHANNEL(S), 1.5M bps, SERIAL COMM CONTROLLER, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 1/51頁 |

| 文件大?。?/td> | 968K |

| 代理商: | ST16C654IJ68 |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

Exar

Corporation 48720 Kato Road, Fremont CA, 94538

(510) 668-7000

FAX (510) 668-7017

www.exar.com

ST16C654/654D

2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO

OCTOBER 2003

REV. 5.0.0

GENERAL DESCRIPTION

The ST16C654/654D

1

(654) is an enhanced quad

Universal Asynchronous Receiver and Transmitter

(UART) each with 64 bytes of transmit and receive

FIFOs, transmit and receive FIFO trigger levels,

automatic hardware and software flow control, and

data rates of up to 1.5 Mbps. Each UART has a set of

registers that provide the user with operating status

and control, receiver error indications, and modem

serial interface controls. Selectable interrupt polarity

provides flexibility to meet design requirements. An

internal

loopback

capability

diagnostics. The 654 is available in 64 pin TQFP 68

pin PLCC and 100 pin QFP packages. The 64 pin

package only offers the 16 mode interface, but the 68

and 100 pin packages offer an additional 68 mode

interface which allows easy integration with Motorola

processors. The ST16C654CQ64 (64 pin) offers

three

state

interrupt

ST16C654DCQ64 provides continuous interrupt

output. The 100 pin package provides additional

FIFO status outputs (TXRDY# and RXRDY# A-D),

separate infrared transmit data outputs (IRTX A-D)

and channel C external clock input (CHCCLK). The

ST16C654/654D is compatible with the industry

standard ST16C454 and ST16C654/554D.

N

OTE

:

1 Covered by U.S. Patent #5,649,122.

allows

onboard

output

while

the

FEATURES

Pin-to-pin compatible with ST16C454, ST16C554

and TI’s TL16C554AFN and TL16C754BFN

Intel or Motorola Data Bus Interface select

Four independent UART channels

I

Register Set Compatible to 16C550

I

Data rates of up to 1.5 Mbps

I

64 Byte Transmit FIFO

I

64 Byte Receive FIFO with error tags

I

4 Selectable TX and RX FIFO Trigger Levels

I

Automatic Hardware (RTS/CTS) Flow Control

I

Automatic Software (Xon/Xoff) Flow Control

I

Progammable Xon/Xoff characters

I

Wireless Infrared (IrDA 1.0) Encoder/Decoder

I

Full modem interface

2.97V to 5.5V supply operation

Sleep Mode (200 uA typical)

Crystal oscillator or external clock input

APPLICATIONS

Portable Appliances

Telecommunication Network Routers

Ethernet Network Routers

Cellular Data Devices

Factory Automation and Process Controls

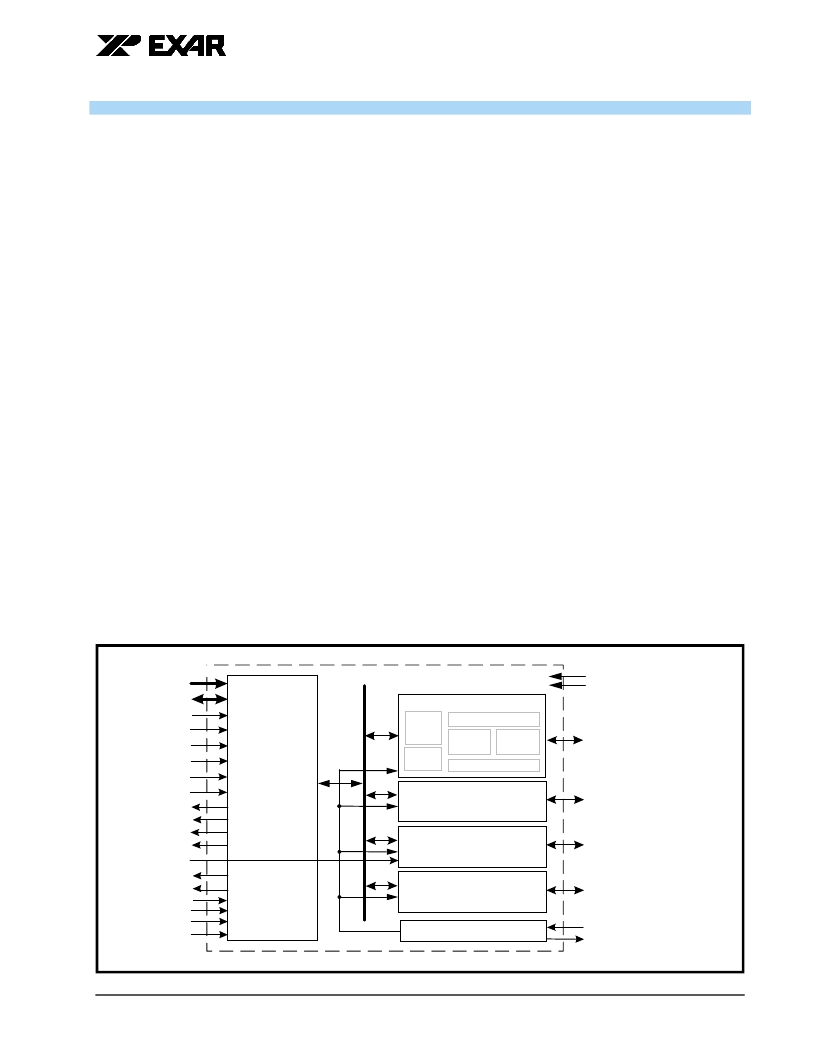

F

IGURE

1. ST16C654 B

LOCK

D

IAGRAM

XTAL1

XTAL2

Crystal Osc/Buffer

Data Bus

Interface

UART Channel A

64 Byte TX FIFO

UART

Regs

64 Byte RX FIFO

BRG

IR

ENDEC

TX & RX

2.97V to 5.5V VCC

GND

654 BLK

TXB, RXB, IRTXB, DTRB#,

DSRB#, RTSB#, CTSB#,

CDB#, RIB#

UART Channel B

(same as Channel A)

A2:A0

D7:D0

IOR#

CSA#

CSB#

CSC#

CSD#

16/68#

INTSEL

CLKSEL

INTA

INTB

INTC

INTD

IOW#

Reset

CHCCLK

TXRDY# A-D

RXRDY# A-D

UART Channel C

(same as Channel A)

TXA, RXA, IRTXA, DTRA#,

DSRA#, RTSA#, CTSA#,

CDA#, RIA#

TXC, RXC, IRTXC, DTRC#,

DSRC#, RTSC#, CTSC#,

CDC#, RIC#

UART Channel D

(same as Channel A)

TXD, RXD, IRTXD, DTRD#,

DSRD#, RTSD#, CTSD#,

CDD#, RID#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST16C654IQ100 | 2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO |

| ST16C654IQ64 | 2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO |

| ST16KF74 | Microcontroller |

| ST16LF74 | Microcontroller |

| ST16MF74 | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST16C654IJ68-F | 功能描述:UART 接口集成電路 QUAD UARTW/64BYTE FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| ST16C654IJ68-F | 制造商:Exar Corporation 功能描述:IC QUAD UART 1.5MBPS 5.5V 68-PLCC |

| ST16C654IJ68TR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 3.3V/5V 68-Pin PLCC T/R 制造商:Exar Corporation 功能描述:2.97V to 5.5V Quad UART with 64 Byte FIFOs PLCC 68 制造商:Exar Corporation 功能描述:ST16C654IJ68TR-F |

| ST16C654IQ | 制造商:Exar Corporation 功能描述: |

| ST16C654IQ100 | 制造商:EXAR 制造商全稱:EXAR 功能描述:QUAD UART WITH 64-BYTE FIFO AND INFRARED (IrDA) ENCODER/DECODER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。