- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385861 > SSTU32865 (NXP Semiconductors N.V.) 1.8 V 28-bit 1:2 registered buffer with parity for DDR2 RDIMM PDF資料下載

參數(shù)資料

| 型號(hào): | SSTU32865 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 1.8 V 28-bit 1:2 registered buffer with parity for DDR2 RDIMM |

| 中文描述: | 1.8伏28位1:2登記緩沖區(qū)的DDR2 RDIMM特別平價(jià) |

| 文件頁(yè)數(shù): | 5/29頁(yè) |

| 文件大?。?/td> | 157K |

| 代理商: | SSTU32865 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

9397 750 13799

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Product data sheet

Rev. 02 — 28 September 2004

5 of 29

Philips Semiconductors

SSTU32865

1.8 V DDR registered buffer with parity

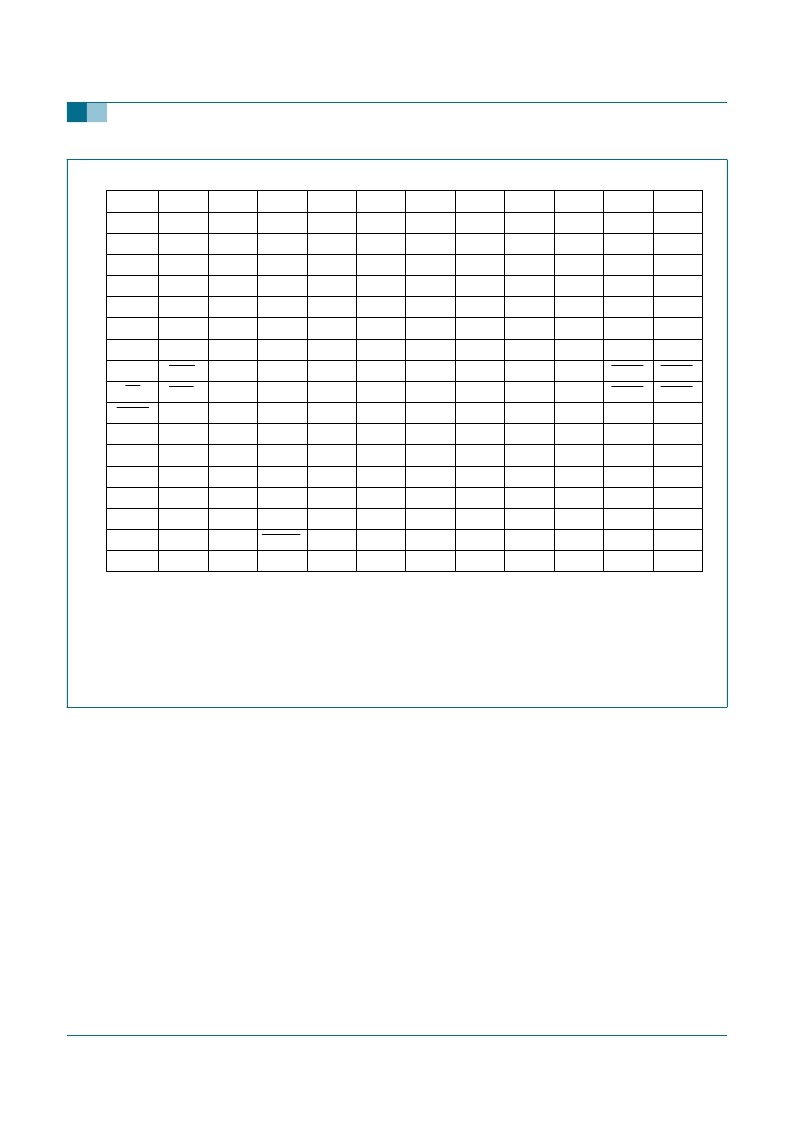

160-ball, 12

×

18 grid; top view.

An empty cell indicates no ball is populated at that grid point.

n.c. denotes a no-connect (ball present but not connected to the die).

m.c.l. denotes a pin that must be connected LOW.

m.c.h. denotes a pin that must be connected HIGH.

Fig 3.

Ball mapping

VREF

n.c.

PARIN

n.c.

n.c.

QCKE1A

1

2

3

4

5

6

D1

D2

n.c.

n.c.

n.c.

QCKE1B

A

B

D3

D4

C

D6

D5

VDDL

GND

n.c.

D

D7

D8

VDDL

GND

VDDL

E

D11

D9

VDDL

GND

F

D18

D12

VDDL

GND

G

CSGATEEN

D15

VDDL

GND

H

CK

DCS0

GND

GND

J

CK

DCS1

VDDL

VDDL

K

D14

GND

GND

L

D0

D10

GND

GND

M

D17

D16

VDDL

VDDL

N

D19

D21

GND

VDDL

VDDL

P

D13

D20

GND

VDDL

VDDL

R

DODT1

DODT0

T

002aab011

QCKE0A

Q21A

Q19A

Q18A

Q17B

Q17A

7

8

9

10

11

12

QCKE0B

Q21B

Q19B

Q18B

QODT0B

QODT0A

QODT1B

QODT1A

n.c.

GND

GND

Q20B

Q20A

VDDR

GND

GND

Q16B

Q16A

VDDR

VDDR

Q1B

Q1A

VDDR

VDDR

Q2B

Q2A

GND

GND

Q5B

Q5A

VDDR

VDDR

QCS0B

QCS0A

GND

GND

QCS1B

QCS1A

VDDR

VDDR

Q6B

Q6A

GND

GND

Q10B

Q10A

VDDR

VDDR

Q9B

Q9A

VDDR

VDDR

GND

Q11B

Q11A

GND

GND

GND

Q15B

Q15A

Q14B

Q14A

DCKE0

DCKE1

m.c.l.

PTYERR

m.c.h.

Q3B

U

VREF

m.c.l.

m.c.l.

n.c.

m.c.h.

Q3A

V

Q12B

Q7B

Q4B

Q13B

Q0B

Q8B

Q12A

Q7A

Q4A

Q13A

Q0A

Q8A

RESET

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SSTU32865EG | Linear Voltage Regulator IC; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No |

| SSTUA32864 | Linear Voltage Regulator IC; Package/Case:8-MSOP; Current Rating:250mA; Leaded Process Compatible:No; Output Voltage Max:1.8V; Peak Reflow Compatible (260 C):No; Reel Quantity:2500; Voltage Regulator Type:Low Dropout (LDO) |

| SSTUA32864EC | Linear Voltage Regulator IC; Package/Case:8-MSOP; Current Rating:250mA; Leaded Process Compatible:No; Output Voltage Max:2.5V; Peak Reflow Compatible (260 C):No; Reel Quantity:2500; Voltage Regulator Type:Low Dropout (LDO) |

| SSTUA32864EG | Linear Voltage Regulator IC; Package/Case:8-MSOP; Current Rating:250mA; Leaded Process Compatible:No; Output Voltage Max:2.8V; Peak Reflow Compatible (260 C):No; Reel Quantity:2500; Voltage Regulator Type:Low Dropout (LDO) |

| SSTVN16859 | 13-bit 1:2 SSTL_2 registered buffer for DDR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SSTU32865EG | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.8 V 28-bit 1:2 registered buffer with parity for DDR2 RDIMM |

| SSTU32865ET | 功能描述:寄存器 1.8V 28-BIT REG BUF/PARITY RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時(shí)鐘頻率:36 MHz 傳播延遲時(shí)間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTU32865ET,518 | 功能描述:寄存器 1.8V 28-BIT REG RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時(shí)鐘頻率:36 MHz 傳播延遲時(shí)間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTU32865ET,551 | 功能描述:寄存器 1.8V 28-BIT REG RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時(shí)鐘頻率:36 MHz 傳播延遲時(shí)間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTU32865ET,557 | 功能描述:寄存器 1.8V 28-BIT REG RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時(shí)鐘頻率:36 MHz 傳播延遲時(shí)間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。