- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1961 > PI7C8154ANAE (Pericom)IC PCI-PCI BRIDGE ASYNC 304-PBGA PDF資料下載

參數(shù)資料

| 型號(hào): | PI7C8154ANAE |

| 廠商: | Pericom |

| 文件頁(yè)數(shù): | 51/114頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC PCI-PCI BRIDGE ASYNC 304-PBGA |

| 標(biāo)準(zhǔn)包裝: | 27 |

| 系列: | * |

| 應(yīng)用: | * |

| 接口: | * |

| 電源電壓: | * |

| 封裝/外殼: | 304-BBGA |

| 供應(yīng)商設(shè)備封裝: | 304-PBGA(31x31) |

| 包裝: | 管件 |

| 安裝類(lèi)型: | 表面貼裝 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)當(dāng)前第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)

PI7C8154A

ASYNCHRONOUS 2-PORT

PCI-to-PCI BRIDGE

Advance Information

Page 41 of 113

DEC 2009 REVISION 1.02

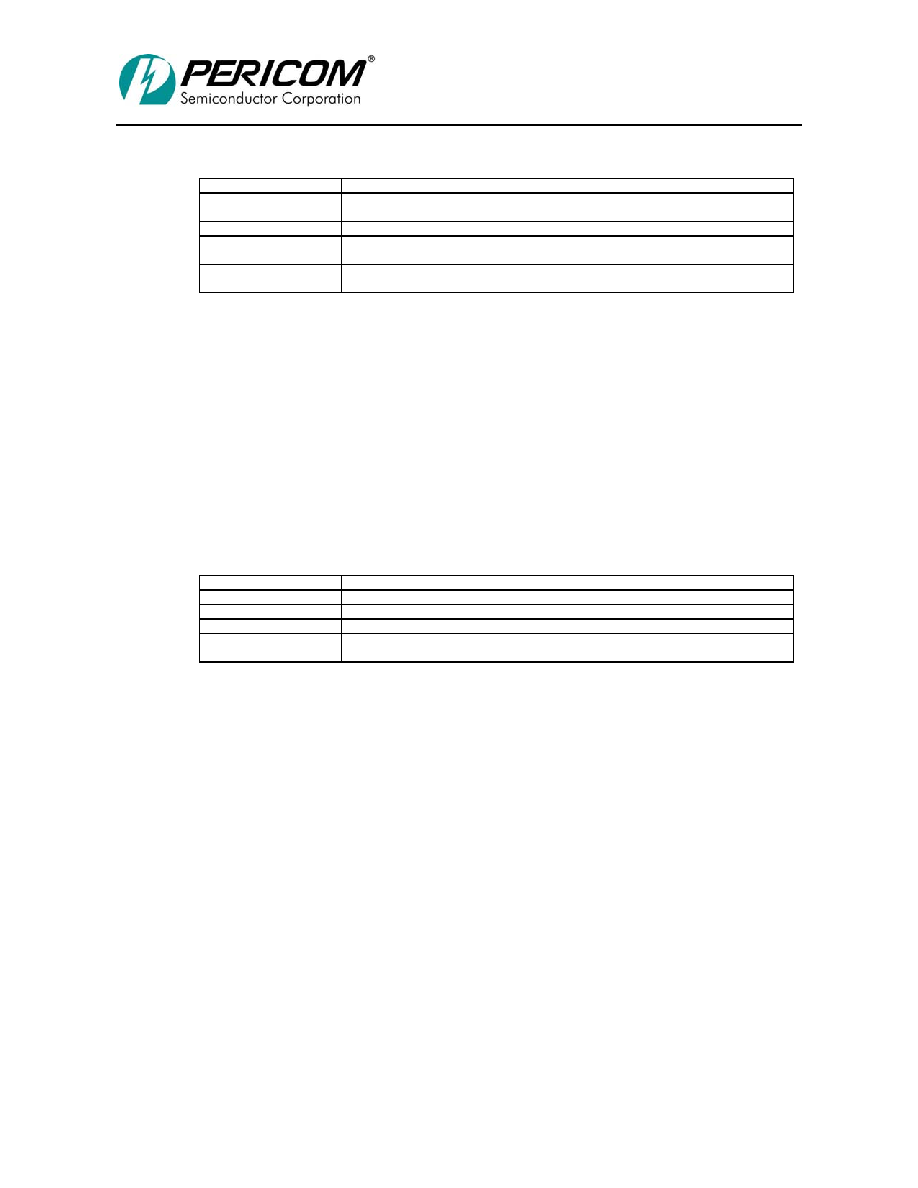

Table 2-7 DELAYED WRITE TARGET TERMINATION RESPONSE

Target Termination

Response

Normal

Returning disconnect to initiator with first data transfer only if multiple data phases

requested.

Target Retry

Returning target retry to initiator. Continue write attempts to target

Target Disconnect

Returning disconnect to initiator with first data transfer only if multiple data phases

requested.

Target Abort

Returning target abort to initiator. Set received target abort bit in target interface status

register. Set signaled target abort bit in initiator interface status register.

After the PI7C8154A makes 224 (default) attempts of the same delayed write trans-action on the

target bus, PI7C8154A asserts P_SERR# if the SERR# enable bit (bit 8 of command register for

the secondary bus) is set and the delayed-write-non-delivery bit is not set. The delayed-write-non-

delivery bit is bit 5 of P_SERR# event disable register (offset 64h). PI7C8154A will report system

error. See Section 5.4 for a description of system error conditions.

2.11.3.2

POSTED WRITE TARGET TERMINATION RESPONSE

When PI7C8154A initiates a posted write transaction, the target termination cannot be passed back

to the initiator. Table 2-8 shows the response to each type of target termination that occurs during a

posted write transaction.

Table 2-8 RESPONSE TO POSTED WRITE TARGET TERMINATION

Target Termination

Repsonse

Normal

No additional action.

Target Retry

Repeating write transaction to target.

Target Disconnect

Initiate write transaction for delivering remaining posted write data.

Target Abort

Set received-target-abort bit in the target interface status register. Assert P_SERR# if

enabled, and set the signaled-system-error bit in primary status register.

Note that when a target retry or target disconnect is returned and posted write data associated with

that transaction remains in the write buffers, PI7C8154A initiates another write transaction to

attempt to deliver the rest of the write data. If there is a target retry, the exact same address will be

driven as for the initial write trans-action attempt. If a target disconnect is received, the address that

is driven on a subsequent write transaction attempt will be updated to reflect the address of the

current DWORD. If the initial write transaction is Memory-Write-and-Invalidate transaction, and a

partial delivery of write data to the target is performed before a target disconnect is received,

PI7C8154A will use the memory write command to deliver the rest of the write data. It is because

an incomplete cache line will be transferred in the subsequent write transaction attempt.

After the PI7C8154A makes 224 (default) write transaction attempts and fails to deliver all posted

write data associated with that transaction, PI7C8154A asserts P_SERR# if the primary SERR#

enable bit is set (bit 8 of command register for secondary bus) and posted-write-non-delivery bit is

not set. The posted-write-non-delivery bit is the bit 2 of P_SERR# event disable register (offset

64h). PI7C8154A will report system error. See Section 5.4 for a discussion of system error

conditions.

2.11.3.3

DELAYED READ TARGET TERMINATION RESPONSE

When PI7C8154A initiates a delayed read transaction, the abnormal target responses can be passed

back to the initiator. Other target responses depend on how much data the initiator requests. Table

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C8154BNAIE | IC PCI-PCI BRIDGE ASYNC 304-PBGA |

| PI7C9X110BNBE | IC PCIE TO PCI REV BRG 160LFBGA |

| PI7C9X130DNDE | IC PCIE-PCIX BRIDGE 1PORT 256BGA |

| PI7C9X20303SLCFDE | IC PCIE PACKET SWITCH 128LQFP |

| PI7C9X20303ULAZPE | IC PCIE PACKET SWITCH 132TQFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C8154ANAE-33 | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 64B/66MHz 2 Port PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C8154B | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:2 PORT 64 BIT 66MHZ PCI TO PCI BRIDGE |

| PI7C8154BNA | 制造商:Pericom Semiconductor Corporation 功能描述: |

| PI7C8154BNAE | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 64B/66MHz 2 Port PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C8154BNAE-80 | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 64B/66MHz 2 Port PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。