- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384801 > OX16CF950 (Electronic Theatre Controls, Inc.) LOW COST ASYNCHRONOUS 16 BIT CARD PDF資料下載

參數(shù)資料

| 型號(hào): | OX16CF950 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | LOW COST ASYNCHRONOUS 16 BIT CARD |

| 中文描述: | 低成本異步16位卡 |

| 文件頁數(shù): | 12/60頁 |

| 文件大小: | 753K |

| 代理商: | OX16CF950 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

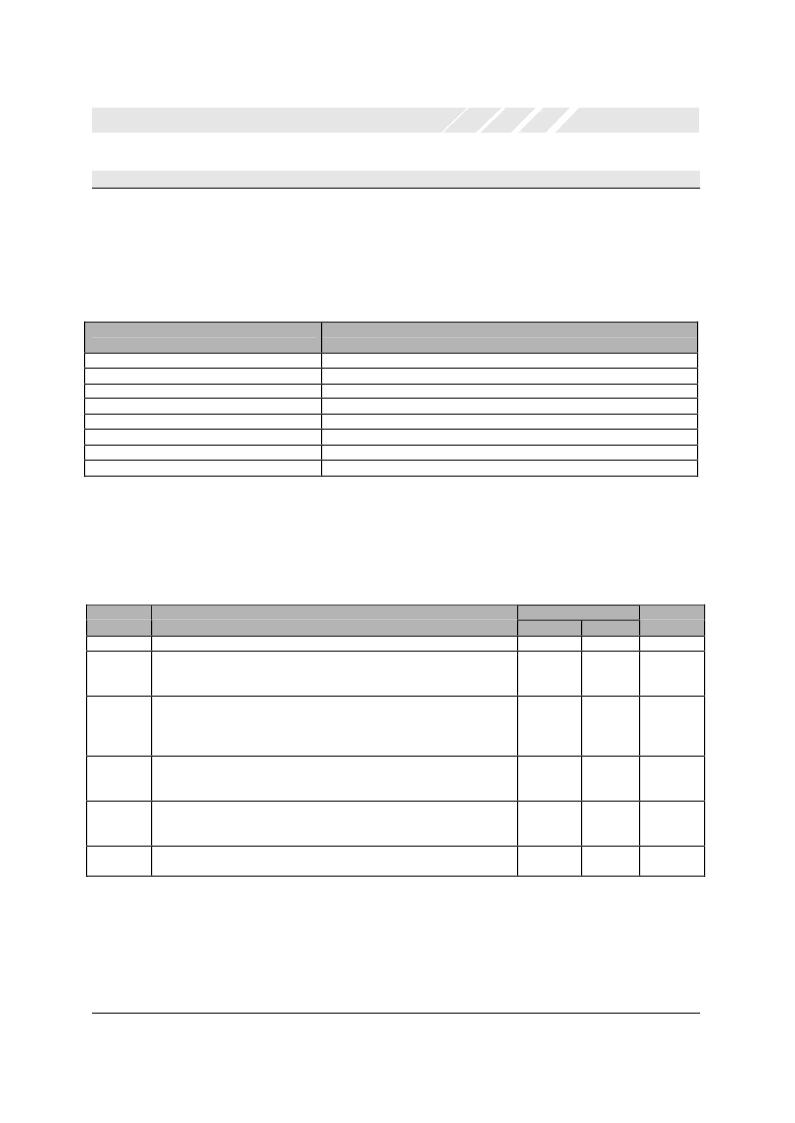

5.3.3

The local configuration registers are a set of device specific registers, which can be accessed via standard IO mapping. As the

device is configured as a single function device, no base address is required to access the local configuration registers. Since IO

mapping is used, access to the local configuration registers is permitted only after the card has been configured. Once the

Configuration Options Register has been set in the Attribute area, the local configuration registers can be accessed following the

mapping shown in Table 5. This access is always permitted in Normal Mode. In Local Bus Mode access is only permitted if bit[0]

is set to ‘1’ in the MDR register in the UART, otherwise the local bus will be accessed rather than the local configuration

registers.

CF/PCMCIA offset from address 0 for local

configuration registers in IO space (hex)

8

EEPROM Status and Control register

9

Multi-Purpose I/O Configuration register

A

UART Divider/Interrupt Pulse Width Divider register

B

Mode Status register

C

Interrupt Status register

D

Soft UART/Local Bus reset register

E

Reserved

F

Reserved

Page 12

OXCF950 DATA SHEET V1.1

OXFORD SEMICONDUCTOR LTD.

Accessing Local Configuration Registers

Register Map

Table 5: Local Configuration Register's mapping in I/O space

Each of the local configuration registers are explained in the following sections

EEPROM Status and Control register ‘ESC’(Offset 0x08)

This register defines the control on the serial EEPROM. The individual bits are described in Table 6.

Bits

Description

Read/Write

EEPROM

-

-

PCMCIA

R

R

Reset

7:5

4

Reserved

EEPROM Data In

.

For reads from the EEPROM this input bit is the output-data (DO) of the

external EEPROM connected to EE_DI pin

EEPROM Data Out

.

For writes to the EEPROM, this output bit feeds the inputdata of the

external EEPROM (DI). This bit is output on the devices EE_DO and

clocked into the EEPROM by EE_CK

EEPROM Clock

.

For reads or writes to the external EEPROM toggle this bit to generate an

EEPROM clock (EE_CK pin)

EEPROM Chip Select

.

When ‘1’ the EEPROM chip select pin EE_CS is activated (high). When ‘0’

EE_CS is de-activated (low)

EEPROM Valid

A ‘1’ indicates that a valid EEPROM program header is present

000

X

3

-

R/W

0

2

-

R/W

0

1

-

R/W

0

0

-

R

X

Table 6: EEPROM Status and Control Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OX2000A | OCXO |

| OX2020A | OCXO |

| OX2420A | OCXO |

| OX4020A | OCXO |

| OX4420A | OCXO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OX16PCI952 | 制造商:OXFORD 制造商全稱:OXFORD 功能描述:Integrated High Performance Dual UARTs, Parallel Port and 5.0v PCI interface |

| OX16PCI952_05 | 制造商:OXFORD 制造商全稱:OXFORD 功能描述:Integrated High Performance Dual UARTs, Parallel Port and 5.0v PCI interface |

| OX16PCI952-TQAG | 制造商:PLX Technology 功能描述: 制造商:Oxford Semiconductor 功能描述:IC PCI BRIDGE DUAL PORT UART SMD |

| OX16PCI952-TQC60-A | 制造商:OXFORD 制造商全稱:OXFORD 功能描述:Integrated High Performance Dual UARTs, Parallel Port and 5.0v PCI interface |

| OX16PCI952-TQFP-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Integrated High Performance Dual UARTs, Parallel Port and 5.0v PCI interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。