- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98045 > MSM82C37B-5GS-2K (OKI ELECTRIC INDUSTRY CO LTD) 4 CHANNEL(S), 5 MHz, DMA CONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | MSM82C37B-5GS-2K |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | DMA控制器 |

| 英文描述: | 4 CHANNEL(S), 5 MHz, DMA CONTROLLER, PQFP44 |

| 封裝: | 9 X 10 MM, 0.80 MM PITCH, PLASTIC, QFP-44 |

| 文件頁數(shù): | 32/34頁 |

| 文件大小: | 327K |

| 代理商: | MSM82C37B-5GS-2K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁

7/33

Semiconductor

MSM82C37B-5RS/GS/VJS

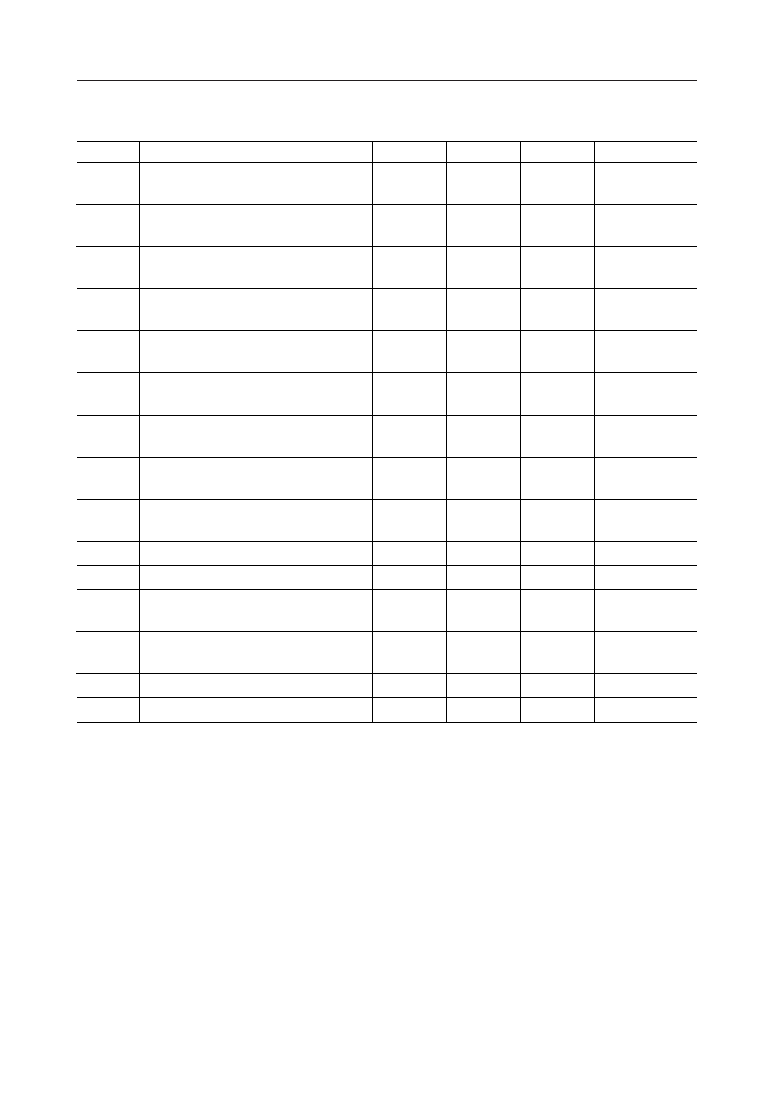

Slave Mode

Item

Symbol

Min.

Max.

Unit

Time from Address Valid or

CS Leading Edge to IOR Leading Edge

Comments

tAR

(Ta = –40 to +85°C, VCC = 4.5 to 5.5 V)

50

—

ns

Address Valid Set-up Time

to IOW Trailing Edge

tAW

130

—

ns

CS Leading Edge Set-up Time

to IOW trailing edge

tCW

130

—

ns

Data Valid Set-up Time

to IOW Trailing Edge

tDW

130

—

ns

Address or CS Hold Time

to IOR Trailing Edge

tRA

0—

—

ns

Data Access Time

to IOR Leading Edge

tRDE

——

140

ns

Delay Time to Data Floating Status

from IOR Trailing Edge

tRDF

0—

70

ns

Supply Power Leading Edge Set-up

time to RESET Trailing Edge

tRSTD

500

—

ns

Time to First Active IOR or IOW

from RESET Trailing Edge

tRSTS

2tCY

—

ns

RESET Pulse Width

tRSTW

300

—

ns

IOR Pulse Width

tRW

200

—

ns

Address Hold Time

to IOW Trailing Edge

tWA

20

—

ns

CS Trailing Edge Hold Time

to IOW Trailing Edge

tWC

20

—

ns

Data Hold Time to IOW Trailing Edge

tWD

30

—

ns

IOW Pulse Width

tWWS

160

—

ns

Notes: 1. Output load capacitance of 150 (pF).

2. IOW and MEMW pulse widths of tCY – 100 (ns) for normal writing, and 2tCY – 100

(ns) for extended writing. IOR and MEMR pulse widths of 2tCY – 50 (ns) for normal

timing, and tCY – 50 (ns) for compressed timing.

3. DREQ and DACK signal active level can be set to either low or high. In the timing

chart, the DREQ signal has been set to active-high, and the DACK signal to active-

low.

4. When the CPU executes continuous read or write in programming mode, the

interval during which the read or write pulse becomes active must be set to at least

400 ns.

5. EOP is an open drain output. The value given is obtained when a 2.2 kW pull-up

resistance is connected to VCC.

6. Rise time and fall time are less than 10 ns.

7. Waveform measurement points for both input and output signals are 2.2 V for HIGH

and 0.8 V for LOW, unless otherwise noted.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM82C37B-5RS | 4 CHANNEL(S), 5 MHz, DMA CONTROLLER, PDIP40 |

| MSM82C37B-5GS-2K | 4 CHANNEL(S), 5 MHz, DMA CONTROLLER, PQFP44 |

| MSM82C43GS-K | 20 I/O, PIA-GENERAL PURPOSE, PDSO24 |

| MSM82C51A-2GS | 1 CHANNEL(S), 64K bps, SERIAL COMM CONTROLLER, PDSO32 |

| MSM82C54-2GS-K | 3 TIMER(S), PROGRAMMABLE TIMER, PDSO32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM82C37B-5JS | 制造商:OK International 功能描述:4 CHANNEL(S), 5 MHZ, DMA CONTROLLER, PQCC44 |

| MSM82C37B-5RS | 制造商:OK International 功能描述:4 CHANNEL(S), 5 MHz, DMA CONTROLLER, PDIP40 |

| MSM82C37B-5VJS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:PROGRAMMABLE DMA CONTROLLER |

| MSM82C43 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:INPUT/OUTPUT PORT EXPANDER |

| MSM82C51A-2GS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。