- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC604E (Motorola, Inc.) PowerPC 604e-TM RISC Microprocessor Technical Summary PDF資料下載

參數(shù)資料

| 型號: | MPC604E |

| 廠商: | Motorola, Inc. |

| 英文描述: | PowerPC 604e-TM RISC Microprocessor Technical Summary |

| 中文描述: | 的PowerPC 604e -商標(biāo)RISC微處理器技術(shù)總結(jié) |

| 文件頁數(shù): | 29/34頁 |

| 文件大?。?/td> | 117K |

| 代理商: | MPC604E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁

PowerPC 604e RISC Microprocessor Technical Summary

29

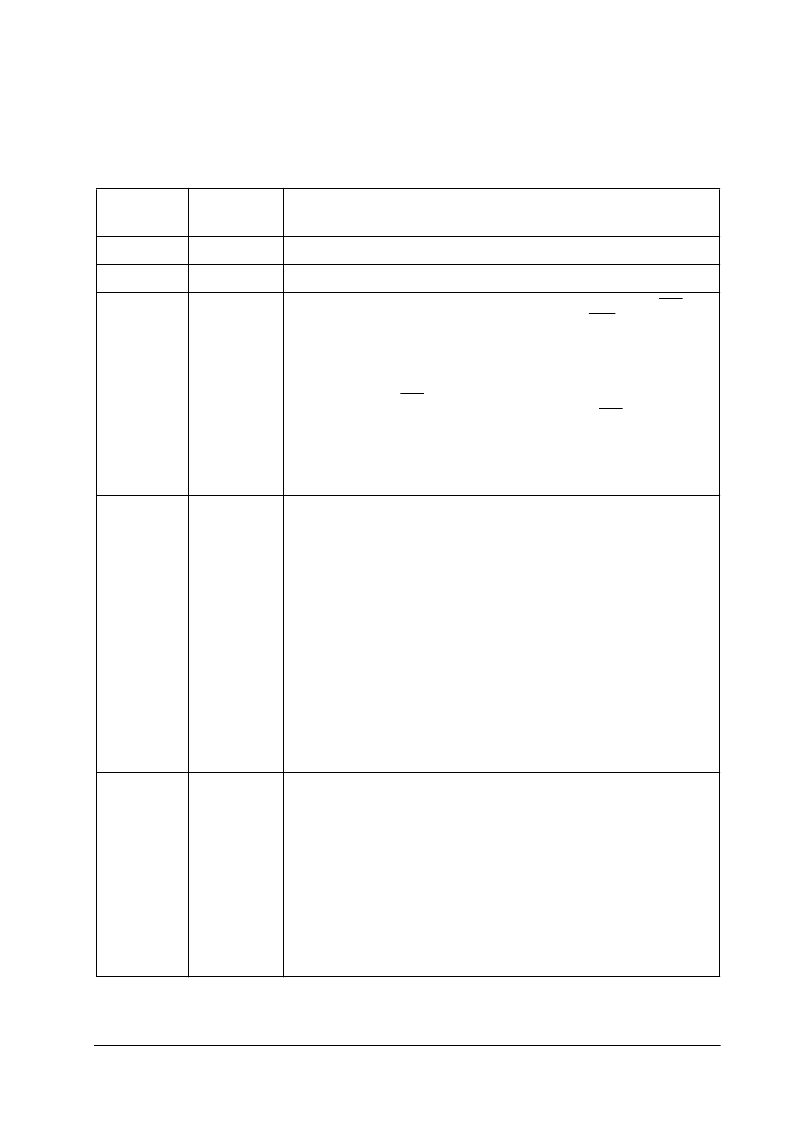

The 604e’s exceptions, and conditions that cause them, are listed in Table 2.

Table 2. Exceptions and Conditions

Exception

Type

Vector Offset

(hex)

Causing Conditions

Reserved

00000

—

System reset

00100

A system reset is caused by the assertion of either the soft or hard reset signal.

Machine

check

00200

A machine check exception is signaled by the assertion of a qualified TEA

indication on the 604e bus, or the machine check input (MCP) signal. If the

MSR[ME] is cleared, the processor enters the checkstop state when one of

these signals is asserted. Note that MSR[ME] is cleared when an exception is

taken. The machine check exception is also caused by parity errors on the

address or data bus or in the instruction or data caches.

The assertion of the TEA signal is determined by load and store operations

initiated by the processor; however, it is expected that the TEA signal would be

used by a memory controller to indicate that a memory parity error or an

uncorrectable memory ECC error has occurred.

Note that the machine check exception is imprecise with respect to the

instruction that originated the bus operation.

DSI

00300

The cause of a DSI exception can be determined by the bit settings in the

DSISR, listed as follows:

0 Set if a load or store instruction results in a direct-store exception;

otherwise cleared.

1 Set if the translation of an attempted access is not found in the primary

table entry group (PTEG), or in the rehashed secondary PTEG, or in the

range of a BAT register; otherwise cleared.

4 Set if a memory access is not permitted by the page or DBAT protection

mechanism; otherwise cleared.

5 If SR[T] = 1, set by an

eciwx

,

ecowx

,

lwarx

, or

stwcx

. instruction;

otherwise cleared. Set by an

eciwx

or

ecowx

instruction if the access is to

an address that is marked as write-through.

6 Set for a store operation and cleared for a load operation.

9 Set if an EA matches the address in the DABR while in one of the three

compare modes.

10 Set if the segment table search fails to find a translation for the effective

address; otherwise cleared.

11 Set if

eciwx

or

ecowx

is used and EAR[E] is cleared.

ISI

00400

An ISI exception is caused when an instruction fetch cannot be performed for

any of the following reasons:

The effective address cannot be translated. That is, a page fault occurred for

this part of the translation, so an ISI exception must be taken to retrieve the

translation from a storage device such as a hard disk drive.

The fetch access is to a direct-store segment.

The fetch access violates memory protection. If the key bits (Ks and Kp) in

the segment register and the PP bits in the PTE or IBAT are set to prohibit

read access, instructions cannot be fetched from this location.

An attempt is made to fetch an instruction from a segment configured as no-

execute; that is, SR[N] = 1.

An attempt is made to fetch an instruction from a block or page configured

as guarded, that is the G bit is set and translation is enabled, MSR[IR] = 1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC755BPX350LE | RISC Microprocessor Hardware Specifications |

| MPC755BRX350LE | RISC Microprocessor Hardware Specifications |

| MPC755CPX400LE | RISC Microprocessor Hardware Specifications |

| MPC755CRX400LE | RISC Microprocessor Hardware Specifications |

| MPC755 | RISC Microprocessor Hardware Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC6071 | 制造商:International Rectifier 功能描述: |

| MPC616 | 制造商:Hammond Manufacturing 功能描述:6" X 16" MAGNET PANEL COVER |

| MPC-628-011B | 制造商:FCI 功能描述: |

| MPC628726C | 制造商:FCI 功能描述:- Bulk |

| MPC-6800 | 制造商:AAEON 制造商全稱:AAEON 功能描述:Intel Ultra Low Voltage Celeron Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。