- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC604E (Motorola, Inc.) PowerPC 604e-TM RISC Microprocessor Technical Summary PDF資料下載

參數(shù)資料

| 型號(hào): | MPC604E |

| 廠商: | Motorola, Inc. |

| 英文描述: | PowerPC 604e-TM RISC Microprocessor Technical Summary |

| 中文描述: | 的PowerPC 604e -商標(biāo)RISC微處理器技術(shù)總結(jié) |

| 文件頁數(shù): | 28/34頁 |

| 文件大小: | 117K |

| 代理商: | MPC604E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁

28

PowerPC 604e RISC Microprocessor Technical Summary

Asynchronous—The OEA portion of the PowerPC architecture defines two types of asynchronous

exceptions:

— Asynchronous, maskable—The PowerPC architecture defines the external interrupt and

decrementer interrupt which are maskable and asynchronous exceptions. In the 604e, and in

many PowerPC processors, the hardware interrupt is generated by the assertion of the Interrupt

(INT) signal, which is not defined by the architecture. In addition, the 604e implements one

additional interrupt, the system management interrupt, which performs similarly to the external

interrupt, and is generated by the assertion of the System Management Interrupt (SMI) signal.

When these exceptions occur, their handling is postponed until all instructions, and any

exceptions associated with those instructions, complete execution.

— Asynchronous, nonmaskable—There are two nonmaskable asynchronous exceptions that are

imprecise: system reset and machine check exceptions. Note that the OEA portion of the

PowerPC architecture, which defines how these exceptions work, does not define the causes or

the signals used to cause these exceptions. These exceptions may not be recoverable, or may

provide a limited degree of recoverability for diagnostic purpose.

The PowerPC architecture defines two bits in the machine state register (MSR)—FE0 and FE1—that

determine how floating-point exceptions are handled. There are four combinations of bit settings, of which

the 604e implements three. These are as follows:

Ignore exceptions mode (FE0 = FE1 = 0). In this mode, the instruction dispatch logic feeds the FPU

as fast as possible and the FPU uses an internal pipeline to allow overlapped execution of

instructions. In this mode, floating-point exception conditions return a predefined value instead of

causing an exception.

Precise interrupt mode (FE0 = 1; FE1 = x). This mode includes both the precise mode and imprecise

recoverable mode defined in the PowerPC architecture. In this mode, a floating-point instruction

that causes a floating-point exception brings the machine to a precise state. In doing so, the 604e

takes floating-point exceptions as defined by the PowerPC architecture.

Imprecise nonrecoverable mode (FE0 = 0; FE1 = 1). In this mode, when a floating-point instruction

causes a floating point exception, the save restore register 0 (SRR0) may point to an instruction

following the instruction that caused the exception.

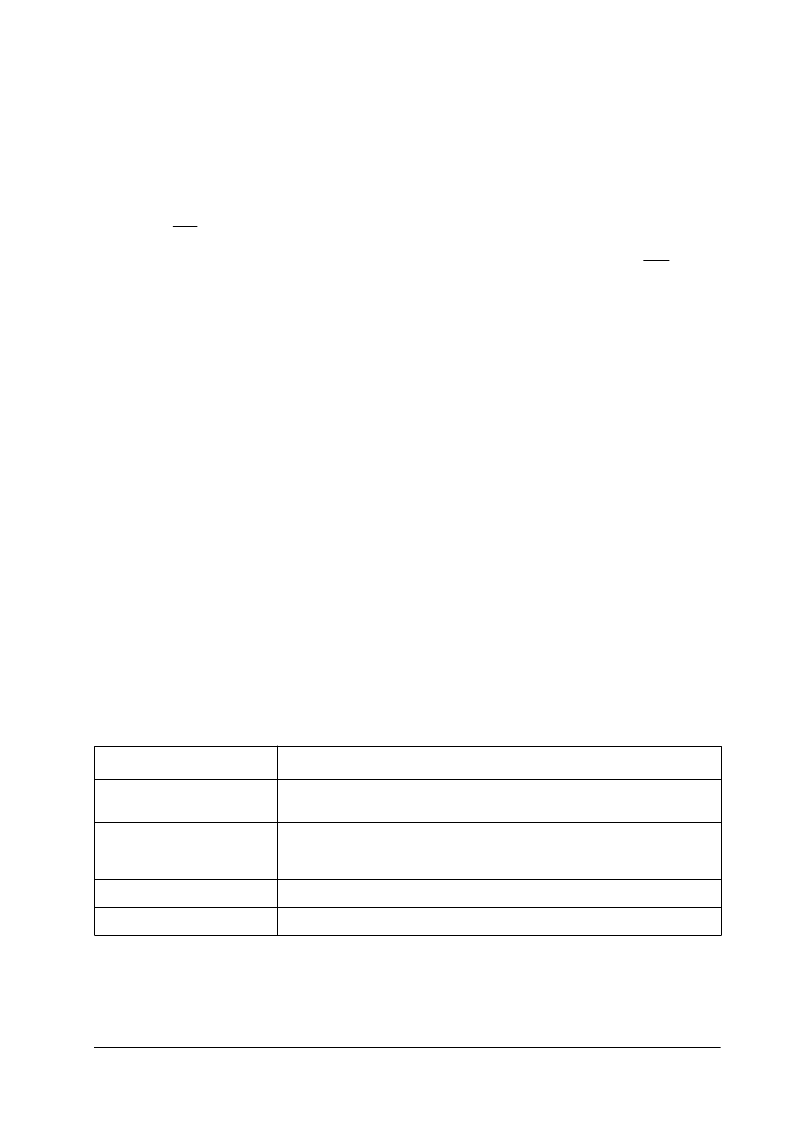

The 604e exception classes are shown in Table 1.

Table 1. Exception Classifications

Type

Exception

Asynchronous/nonmaskable

Machine check

System reset

Asynchronous/maskable

External interrupt

Decrementer

System management interrupt (not defined by the PowerPC architecture)

Synchronous/precise

Instruction-caused exceptions

Synchronous/imprecise

Floating-point exceptions (imprecise nonrecoverable mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC755BPX350LE | RISC Microprocessor Hardware Specifications |

| MPC755BRX350LE | RISC Microprocessor Hardware Specifications |

| MPC755CPX400LE | RISC Microprocessor Hardware Specifications |

| MPC755CRX400LE | RISC Microprocessor Hardware Specifications |

| MPC755 | RISC Microprocessor Hardware Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC6071 | 制造商:International Rectifier 功能描述: |

| MPC616 | 制造商:Hammond Manufacturing 功能描述:6" X 16" MAGNET PANEL COVER |

| MPC-628-011B | 制造商:FCI 功能描述: |

| MPC628726C | 制造商:FCI 功能描述:- Bulk |

| MPC-6800 | 制造商:AAEON 制造商全稱:AAEON 功能描述:Intel Ultra Low Voltage Celeron Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。