- 您現(xiàn)在的位置:買賣IC網 > PDF目錄371051 > MC68HC11KW1 (MOTOROLA INC) High-density complementary metal oxide semiconductor HCMOS) microcontroller unit PDF資料下載

參數(shù)資料

| 型號: | MC68HC11KW1 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | High-density complementary metal oxide semiconductor HCMOS) microcontroller unit |

| 中文描述: | 8-BIT, EEPROM, 4 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁數(shù): | 51/238頁 |

| 文件大小: | 798K |

| 代理商: | MC68HC11KW1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁

MC68HC11KW1

MOTOROLA

4-7

OPERATING MODES AND ON-CHIP MEMORY

4

A/D result 3 (ADR3) high

$0044

(Bit 15)

(14)

(13)

(12)

(11)

(10)

(9)

(8)

undefined

A/D result 3 (ADR3) low

$0045

(7)

(6)

0

0

0

0

0

0

uu00 0000

A/D result 4 (ADR4) high

$0046 (Bit 15)

(14)

(13)

(12)

(11)

(10)

(9)

(8)

undefined

A/D result 4 (ADR4) low

$0047

(7)

(6)

0

0

0

0

0

0

uu00 0000

A/D result 5 (ADR5) high

$0048

(Bit 15)

(14)

(13)

(12)

(11)

(10)

(9)

(8)

undefined

A/D result 5 (ADR5) low

$0049

(7)

(6)

0

0

0

0

0

0

uu00 0000

A/D result 6 (ADR6) high

$004A (Bit 15)

(14)

(13)

(12)

(11)

(10)

(9)

(8)

undefined

A/D result 6 (ADR6) low

$004B

(7)

(6)

0

0

0

0

0

0

uu00 0000

A/D result 7 (ADR7) high

$004C

(Bit 15)

(14)

(13)

(12)

(11)

(10)

(9)

(8)

undefined

A/D result 7 (ADR7) low

$004D

(7)

(6)

0

0

0

0

0

0

uu00 0000

A/D result 8 (ADR8) high

$004E

(Bit 15)

(14)

(13)

(12)

(11)

(10)

(9)

(8)

undefined

A/D result 8 (ADR8) low

$004F

(7)

(6)

0

0

0

0

0

0

uu00 0000

Reserved

$0050

Reserved

$0051

Reserved

$0052

Reserved

$0053

Reserved

$0054

Reserved

$0055

Memory mapping window size

(MMSIZ)

$0056 MXGS2MXGS1W2SZ1 W2SZ0

0

0

W1SZ1 W1SZ0 0000 0000

Memory mapping window base (MMWBR)

$0057 W2A15 W2A14 W2A13

0

W1A15 W1A14 W1A13

0

0000 0000

Memory mapping window 1 control

(MM1CR)

$0058

0

X1A18 X1A17 X1A16 X1A15 X1A14 X1A13

0

0000 0000

Memory mapping window 2 control

(MM2CR)

$0059

0

X2A18 X2A17 X2A16 X2A15 X2A14 X2A13

0

0000 0000

Chip select clock stretch (CSCSTR)

$005A

IOSA

IOSB GP1SA GP1SB GP2SA GP2SB PCSA PCSB 0000 000x

Chip select control (CSCTL)

$005B

IOEN

IOPL IOCSA IOSZ GCSPRPCSENPCSZA PCSZB 0000 0100

Gen. purpose chip select 1 addr. (GPCS1A)

$005C G1A18 G1A17 G1A16 G1A15 G1A14 G1A13 G1A12 G1A11 0000 0000

Gen. purpose chip select 1 con. (GPCS1C)

$005D G1DG2G1DPC G1POL G1AV G1SZA G1SZB G1SZC G1SZD 0000 0000

Gen. purpose chip select 2 addr. (GPCS2A)

$005E

G2A18 G2A17 G2A16 G2A15 G2A14 G2A13 G2A12 G2A11 0000 0000

Gen. purpose chip select 2 con. (GPCS2C)

$005F

0

G2DPC G2POL G2AV G2SZA G2SZB G2SZC G2SZD 0000 0000

Pulse width clock select (PWCLK)

$0060 CON34 CON12 PCKA2 PCKA1

0

PCKB3 PCKB2 PCKB1 0000 0000

Pulse width polarity select (PWPOL)

$0061 PCLK4 PCLK3 PCLK2 PCLK1 PPOL4 PPOL3 PPOL2 PPOL1 0000 0000

Pulse width scale (PWSCAL)

$0062

(bit 7)

(6)

(5)

(4)

(3)

(2)

(1)

(bit 0) 0000 0000

Pulse width enable (PWEN)

$0063 TPWSL DISCP

0

0

PWEN4PWEN3PWEN2PWEN1 0000 0000

Pulse width count 1 (PWCNT1)

$0064

(bit 7)

(6)

(5)

(4)

(3)

(2)

(1)

(bit 0) 0000 0000

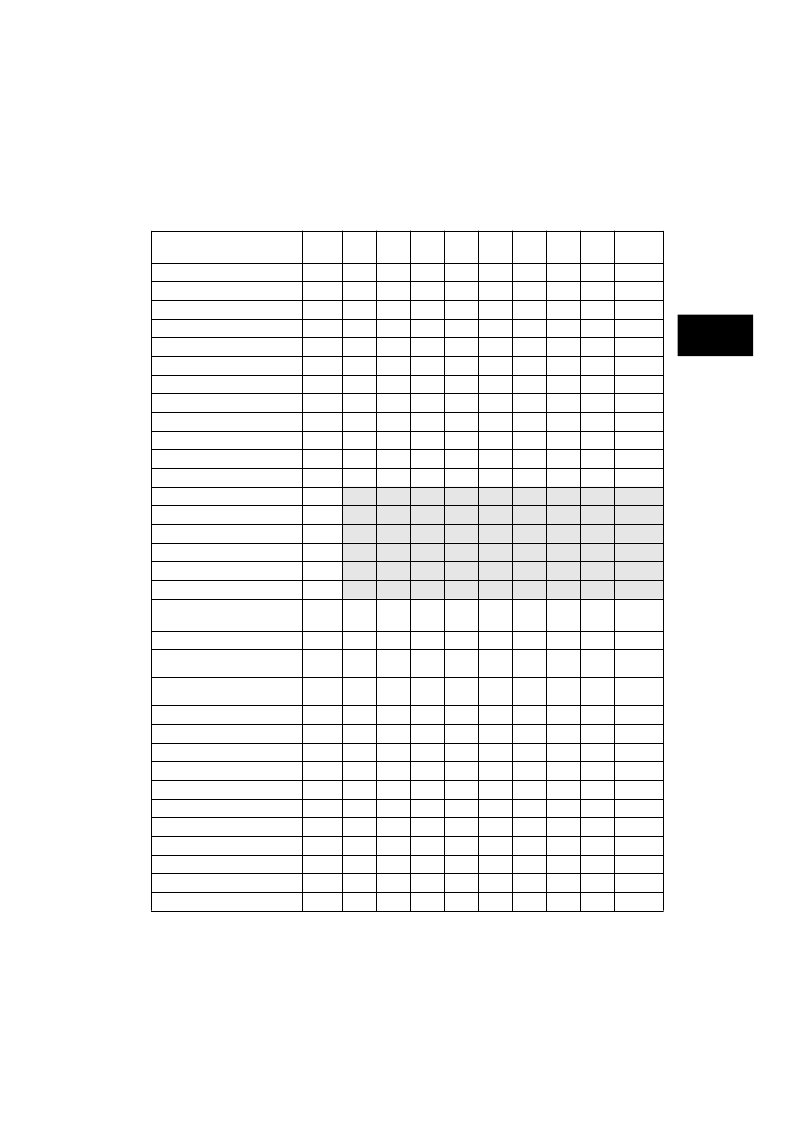

Table 4-2

Register and control bit assignments (Page 3 of 5)

Register name

Address

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

State

on reset

TPG

49

相關PDF資料 |

PDF描述 |

|---|---|

| MC68HC11L6CFN | HCMOS MICROCONTROLLER UNIT |

| MC68HC11L6FS | HCMOS MICROCONTROLLER UNIT |

| MC68HC11L6FU | HCMOS MICROCONTROLLER UNIT |

| MC68HC11L6L | HCMOS MICROCONTROLLER UNIT |

| MC68HC11L6MFB | HCMOS MICROCONTROLLER UNIT |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC11L0 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:CONFIG Register Programming for EEPROM-based M68HC11 Microcontrollers |

| MC68HC11L0CFN2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNIT |

| MC68HC11L0CFN3 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNIT |

| MC68HC11L0CFU2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNIT |

| MC68HC11L0CFU3 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNIT |

發(fā)布緊急采購,3分鐘左右您將得到回復。