- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180218 > M48T129V-70CS1 (STMICROELECTRONICS) 0 TIMER(S), REAL TIME CLOCK, PDSO32 PDF資料下載

參數(shù)資料

| 型號: | M48T129V-70CS1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 時鐘/數(shù)據(jù)恢復及定時提取 |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO32 |

| 封裝: | 8 X 20 MM, PLASTIC, TSOP-32 |

| 文件頁數(shù): | 18/22頁 |

| 文件大?。?/td> | 140K |

| 代理商: | M48T129V-70CS1 |

5/22

M48T129Y, M48T129V

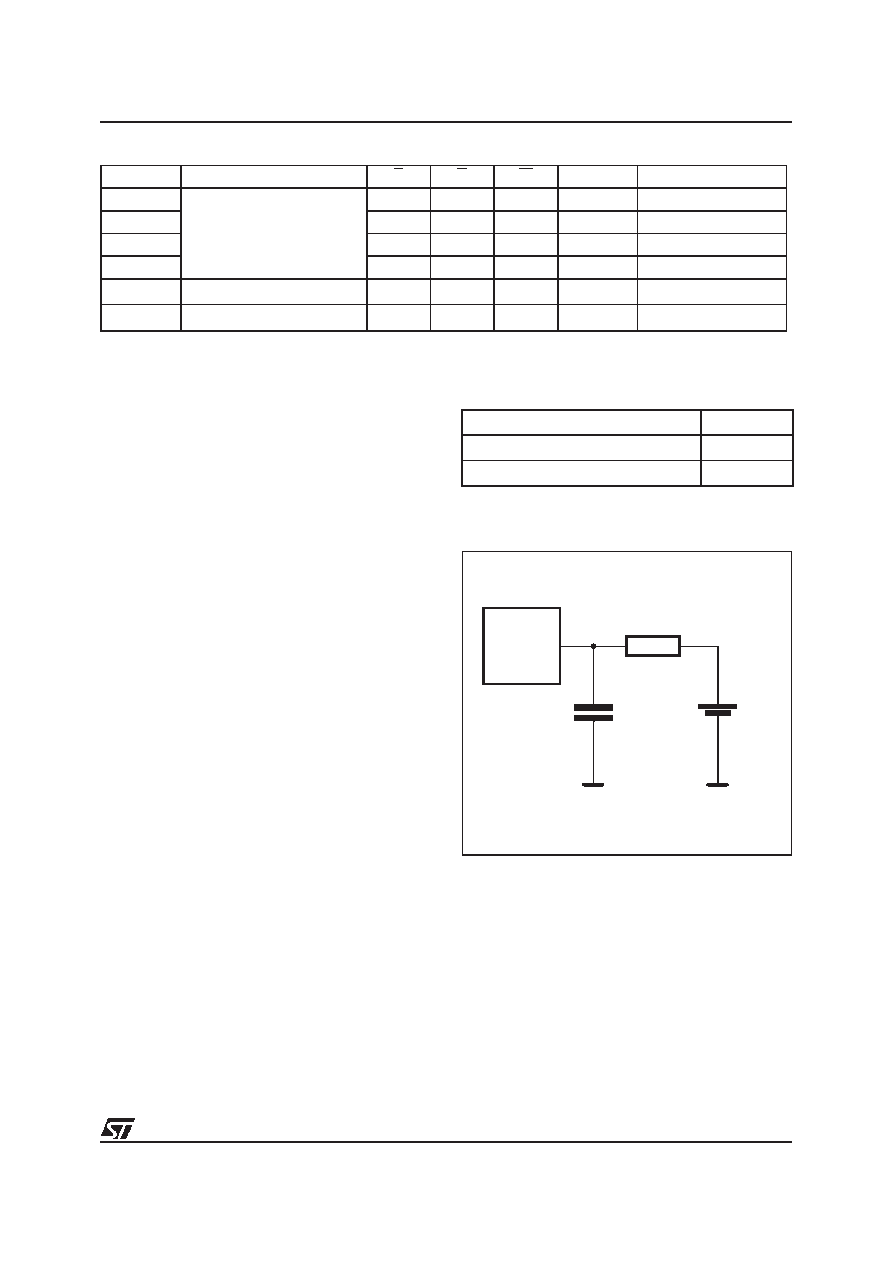

Table 4. AC Measurement Conditions

Note that Output Hi-Z is defined as the point where data is no longer

driven.

Input Rise and Fall Times

≤ 5ns

Input Pulse Voltages

0 to 3V

Input and Output Timing Ref. Voltages

1.5V

Figure 5. AC Testing Load Circuit

Note: Excluding open drain output pins

AI01803C

CL = 100pF

CL includes JIG capacitance

650

DEVICE

UNDER

TEST

1.75V

Table 3. Operating Modes (1)

Note: 1. X = VIH or VIL;VSO = Battery Back-up Switchover Voltage.

2. See Table 7 for details.

Mode

VCC

E

G

W

DQ0-DQ7

Power

Deselect

4.5V to 5.5V

or

3.0V to 3.6V

VIH

X

High Z

Standby

Write

VIL

X

VIL

DIN

Active

Read

VIL

VIH

DOUT

Active

Read

VIL

VIH

High Z

Active

Deselect

VSO to VPFD (min)

(2)

X

High Z

CMOS Standby

Deselect

≤ VSO (2)

X

High Z

Battery Back-up Mode

external copies are independent of internal func-

tions except that they are updated periodically by

the simultaneous transfer of the incremented inter-

nal copy. TIMEKEEPER and Alarm Registers

store data in BCD.

DATA RETENTION MODE

With valid VCC applied, the M48T129Y/V operates

as a conventional BYTEWIDE

static RAM.

Should the supply voltage decay, the RAM will au-

tomatically deselect, write protecting itself when

VCC falls between VPFD (max), VPFD (min) win-

dow. All outputs become high impedance and all

inputs are treated as ”don’t care”.

Note: A power failure during a write cycle may cor-

rupt data at the current addressed location, but

does not jeopardize the rest of the RAM’s content.

At voltages below VPFD (min), the memory will be

in a write protected state, provided the VCC fall

time is not less than tF. The M48T129Y/V may re-

spond to transient noise spikes on VCC that cross

into the deselect window during the time the de-

vice is sampling VCC. Therefore, decoupling of the

power supply lines is recommended.

When VCC drops below VSO, the control circuit

switches power to the internal battery, preserving

data and powering the clock. The internal energy

source will maintain data in the M48T129Y/V for

an accumulated period of at least 10 years at room

temperature. As system power rises above VSO,

the battery is disconnected, and the power supply

is switched to external VCC. Deselect continues for

tREC after VCC reaches VPFD (max). For a further

more detailed review of lifetime calculations,

please see Application Note AN1012.

TIMEKEEPER REGISTERS

The M48T129Y/V offers 16 internal registers

which contain TIMEKEEPER, Alarm, Watchdog,

Interrupt, Flag, and Control data. These registers

are memory locations which contain external (user

accessible) and internal copies of the data (usually

referred to as BiPORT TIMEKEEPER cells). The

相關PDF資料 |

PDF描述 |

|---|---|

| M48T8-150PC1 | REAL TIME CLOCK, PDIP28 |

| M48Z02-150PC6 | 2K X 8 NON-VOLATILE SRAM MODULE, 150 ns, PDIP24 |

| M49142/05-0016 | PANEL MOUNT, CABLE TERMINATED, FEMALE, TRIAXIAL CONNECTOR, CRIMP, RECEPTACLE |

| M49142/05-0116 | PANEL MOUNT, CABLE TERMINATED, FEMALE, TRIAXIAL CONNECTOR, CRIMP, RECEPTACLE |

| M49142/05-0216 | PANEL MOUNT, CABLE TERMINATED, FEMALE, TRIAXIAL CONNECTOR, CRIMP, RECEPTACLE |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M48T129V-70PM1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5.0 or 3.3V, 1 Mbit (128 Kbit x 8) TIMEKEEPER SRAM |

| M48T129V-85CS1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129V-85PM1 | 功能描述:實時時鐘 1M (128Kx8) 85ns RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| M48T129VPM | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129VSH | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。