- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180218 > M48T129V-70CS1 (STMICROELECTRONICS) 0 TIMER(S), REAL TIME CLOCK, PDSO32 PDF資料下載

參數(shù)資料

| 型號: | M48T129V-70CS1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 時鐘/數(shù)據(jù)恢復(fù)及定時提取 |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO32 |

| 封裝: | 8 X 20 MM, PLASTIC, TSOP-32 |

| 文件頁數(shù): | 17/22頁 |

| 文件大?。?/td> | 140K |

| 代理商: | M48T129V-70CS1 |

M48T129Y, M48T129V

4/22

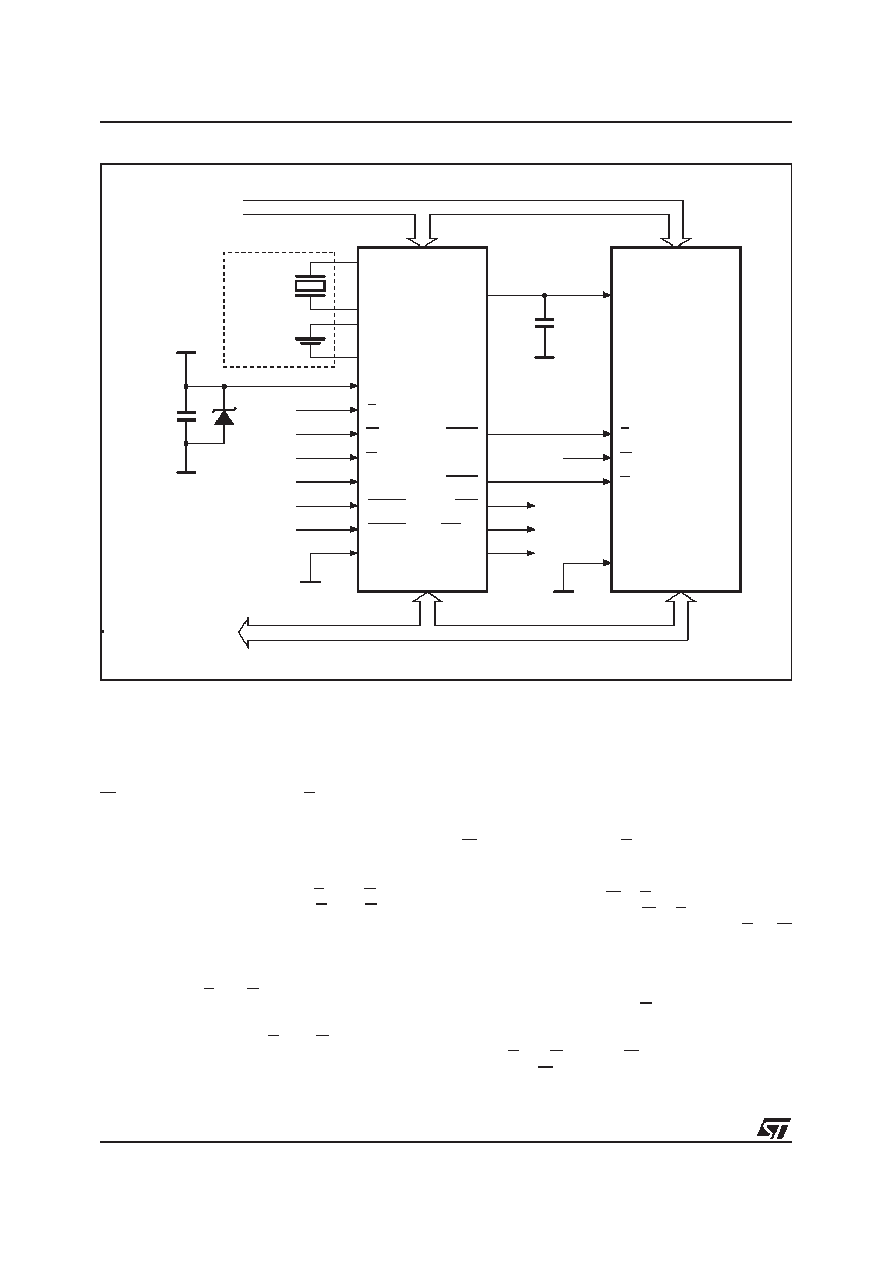

Figure 4. Hardware Hookup for SMT Chip Set (1)

Note: 1. For pin connections, see individual data sheets for M48T201Y/V and M68Z128/W at www.st.com.

2. For 5V, M48T129Y (M48T201Y + M68Z128). For 3.3V, M48T129V (M48T201V + M68Z128W).

3. SNAPHAT Top ordered separately.

AI03632

32,768 Hz

CRYSTAL

LITHIUM

CELL

A0-A16

DQ0-DQ7

E

VCC

W

G

WDI

RSTIN1

RSTIN2

VSS

E

W

G

VCC

VSS

A0-A16

DQ0-DQ7

0.1

F

0.1

F

5V

ECON

GCON

RST

IRQ/FT

SQW

M48T201Y/V

(2)

M68Z128/W

(2)

VOUT

SNAPHAT (3)

BATTERY/CRYSTAL

READ MODE

The M48T129Y/V is in the Read Mode whenever

W (Write Enable) is high and E (Chip Enable) is

low. The unique address specified by the 17 Ad-

dress Inputs defines which one of the 131,072

bytes of data is to be accessed. Valid data will be

available at the Data I/O pins within tAVQV (Ad-

dress Access Time) after the last address input

signal is stable, providing the E and G access

times are also satisfied. If the E and G access

times are not met, valid data will be available after

the latter of the Chip Enable Access Times (tELQV)

or Output Enable Access Time (tGLQV).

The state of the eight three-state Data I/O signals

is controlled by E and G. If the outputs are activat-

ed before tAVQV, the data lines will be driven to an

indeterminate state until tAVQV. If the Address In-

puts are changed while E and G remain active,

output data will remain valid for tAXQX (Output

Data Hold Time) but will go indeterminate until the

next Address Access.

WRITE MODE

The M48T129Y/V is in the Write Mode whenever

W (Write Enable) and E (Chip Enable) are low

state after the address inputs are stable.

The start of a write is referenced from the latter oc-

curring falling edge of W or E. A write is terminated

by the earlier rising edge of W or E. The addresses

must be held valid throughout the cycle. E or W

must return high for a minimum of tEHAX from Chip

Enable or tWHAX from Write Enable prior to the ini-

tiation of another read or write cycle. Data-in must

be valid tDVWH prior to the end of write and remain

valid for tWHDX afterward. G should be kept high

during write cycles to avoid bus contention; al-

though, if the output bus has been activated by a

low on E and G a low on W will disable the outputs

tWLQZ after W falls.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M48T8-150PC1 | REAL TIME CLOCK, PDIP28 |

| M48Z02-150PC6 | 2K X 8 NON-VOLATILE SRAM MODULE, 150 ns, PDIP24 |

| M49142/05-0016 | PANEL MOUNT, CABLE TERMINATED, FEMALE, TRIAXIAL CONNECTOR, CRIMP, RECEPTACLE |

| M49142/05-0116 | PANEL MOUNT, CABLE TERMINATED, FEMALE, TRIAXIAL CONNECTOR, CRIMP, RECEPTACLE |

| M49142/05-0216 | PANEL MOUNT, CABLE TERMINATED, FEMALE, TRIAXIAL CONNECTOR, CRIMP, RECEPTACLE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M48T129V-70PM1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5.0 or 3.3V, 1 Mbit (128 Kbit x 8) TIMEKEEPER SRAM |

| M48T129V-85CS1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129V-85PM1 | 功能描述:實時時鐘 1M (128Kx8) 85ns RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| M48T129VPM | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129VSH | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。