- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370849 > M37905M4C-XXXFP (Mitsubishi Electric Corporation) 16 BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | M37905M4C-XXXFP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 16 BIT CMOS MICROCOMPUTER |

| 中文描述: | 16位CMOS微機(jī) |

| 文件頁數(shù): | 51/102頁 |

| 文件大?。?/td> | 881K |

| 代理商: | M37905M4C-XXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當(dāng)前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

51

M37905M4C-XXXFP, M37905M4C-XXXSP

M37905M6C-XXXFP, M37905M6C-XXXSP

M37905M8C-XXXFP, M37905M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

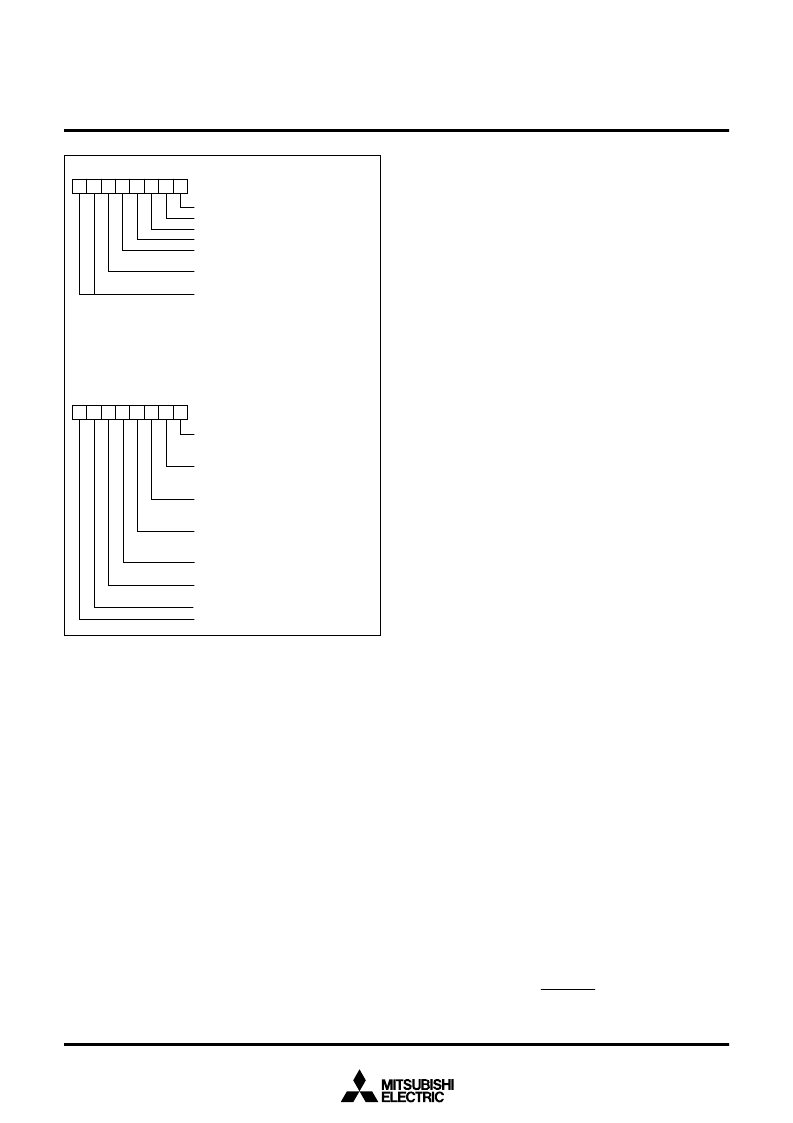

Fig. 57 Bit configuration of pulse output data registers 1 and 0 in

pulse output port mode 1

Pulse mode 0

This mode divides a pulse output port into 4 bits and 4 bits and indi-

vidually controls them.

When setting the pulse output mode select bit to

“

0

”

, and setting bits

2 and 1 to

“

0

”

and bit 0 to

“

1

”

of the waveform output select bits, four

of RTP2

3

, RTP2

2

, RTP2

1

, and RTP2

0

become the pulse output ports

(RTP2 selected).

When setting the pulse output mode select bit to

“

0

”

, and setting bits

2 and 0 to

“

0

”

and bit 1 to

“

1

”

of the waveform output select bits, four

of RTP3

3,

RTP3

2,

RTP3

1

, RTP3

0

become the pulse output ports

(RTP3 selected).

When setting the pulse output mode select bit to

“

0

”

, and setting bit 2

to

“

0

”

and bits 1 and 0 to

“

1

”

of the waveform output select bits, the

following two groups become the pulse output ports:

Four of RTP3

3

, RTP3

2

, RTP3

1

, RTP3

0

Four of RTP2

3

, RTP2

2

, RTP2

1

, RTP2

0

.

Each time the contents of timer A8 counter become 0000

16

, the con-

tents of the pulse output data register 1 (address A4

16

)

’

s high-order

4 bits (bits 7 to 4), which corresponding to RTP3

3

, RTP3

2,

RTP3

1

,

RTP3

0

, are output from ports.

Each time the contents of timer A5 counter become 0000

16

, the con-

tents of pulse output data register 0 (address A2

16

)

’

s low-order 4 bits

(bits 3 to 0), which corresponding to RTP2

3

, RTP2

2

, RTP2

1

, RTP2

0

,

are output from ports.

When writing

“

0

”

to the specified one of the pulse output data bits,

“

L

”

level is output from the pulse output port when the contents of the

corresponding timer counter become 0000

16

; when writing

“

1

”

to it,

“

H

”

level is output from the pulse output port.

In the case that an input trigger of pin RTP

TRG1

is selected, the data

written to the pulse output data bit is output from the corresponding

pulse output port by this selected trigger.

Additionally, pulse width modulation can be applied for RTP2

3

,

RTP2

2

, RTP2

1

, and RTP2

0

. Because timer A6 is used for pulse

width modulation, actuate timer A6 in the pulse width modulation

mode. When any of pulse output data bits is

“

1

”

, the pulse to which

pulse width modulation has been applied is output from the pulse

output port when the contents of timer A5 counter become 0000

16

.

The pulse width modulation using timer A6 can be applied by setting

the pulse width modulation enable bit 0 of the pulse output data reg-

ister 1 (bit 0 at address A4

16

) to

“

1

”

and the pulse width modulation

timer select bits of the pulse output control register (bits 5 and 4 at

address A0

16

) to

“

00

”

. Figure 58 shows example waveforms in pulse

mode 0.

In ports selecting pulse mode 0, output of RTP3

3

, RTP3

2

, RTP3

1

and RTP3

0

is controlled by the waveform output control bit 0 (bit 6)

of pulse output control register; output of RTP2

3

, RTP2

2

, RTP2

1

and

RTP2

0

is done by the waveform output control bit 1 (bit 7).

When setting the waveform output control bit to

“

1

”

, waveform is out-

put from the corresponding port. When clearing that bit to

“

0

”

, wave-

form output from the corresponding port stops, and the port

becomes floating. The waveform output control bits are cleared to

“

0

”

by reset or by executing instructions.

Also, the waveform output control bit 1 can be cleared to

“

0

”

by in-

putting a falling edge to pin P4OUT

CUT

.

RTP2

0

pulse output data bit

RTP2

1

pulse output data bit

RTP2

2

pulse output data bit

RTP2

3

pulse output data bit

RTP3

0

pulse output data bit;

Valid when pulse mode 1 is selected.

RTP3

1

pulse output data bit;

Valid when pulse mode 1 is selected.

Pulse output trigger select bits

0 0 : Underflow of timer A5

0 1 : Falling edge of input signal to pin

RTP

TRG1

1 0 : Rising edge of input signal to pin

RTP

TRG1

1 1 : Falling and rising edges of input

signal to pin RTP

TRG1

7

6

5

4

3

2

1

0

Address

A2

16

Pulse output data register 1

7

6

5

4

3

2

1

0

Address

A4

16

Pulse output data register 0

Pulse width modulation enable bit 0

0 : No pulse width modulation by timer A6

1 : Pulse width modulation by timer A6

Pulse width modulation enable bit 1

0 : No pulse width modulation by timer A7

1 : Pulse width modulation by timer A7

Pulse width modulation enable bit 2

0 : No pulse width modulation by timer A9

1 : Pulse width modulation by timer A9

Pulse output polarity select bit

0 : Positive

1 : Negative

RTP3

0

pulse output data bit;

Valid when pulse mode 0 is selected.

RTP3

1

pulse output data bit;

Valid when pulse mode 0 is selected.

RTP3

2

pulse output data bit

RTP3

3

pulse output data bit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37905M4C-XXXSP | 16 BIT CMOS MICROCOMPUTER |

| M37905M6C-XXXFP | DIODE SCHOTTKY DUAL-DUAL SERIES 25V 200mW 0.32V-vf 200mA-IFM 1mA-IF 2uA-IR SOT-363 3K/REEL |

| M37905M6C-XXXSP | DIO, BAT54C, DUAL SHOTTKEY, COMMON CATHODE, SOT23 |

| M37905M8C-XXXFP | 16 BIT CMOS MICROCOMPUTER |

| M37905M8C-XXXSP | DIODE SCHOTTKY DUAL COMMON-CATHODE 25V 200mW 0.32V-vf 200mA-IFM 1mA-IF 2uA-IR SOT-23 3K/REEL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37905M4C-XXXSP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16 BIT CMOS MICROCOMPUTER |

| M37905M6C-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16 BIT CMOS MICROCOMPUTER |

| M37905M6C-XXXSP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16 BIT CMOS MICROCOMPUTER |

| M37905M8C-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16 BIT CMOS MICROCOMPUTER |

| M37905M8C-XXXSP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16 BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。