- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384544 > ISPPAC-CLK5610V-01T100I (Lattice Semiconductor Corporation) Linear Array Light; LED Color:Blue; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:1.6A; Supply Voltage:24VDC; Wavelength:470nm PDF資料下載

參數(shù)資料

| 型號: | ISPPAC-CLK5610V-01T100I |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | Linear Array Light; LED Color:Blue; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:1.6A; Supply Voltage:24VDC; Wavelength:470nm |

| 中文描述: | 在系統(tǒng)可編程,零延遲時鐘發(fā)生器通用扇出緩沖器 |

| 文件頁數(shù): | 15/47頁 |

| 文件大?。?/td> | 871K |

| 代理商: | ISPPAC-CLK5610V-01T100I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

Lattice Semiconductor

ispClock5600 Family Data Sheet

15

match. The option of which mode to use is programmable and may be set using PAC-Designer software (available

from the Lattice web site at www.latticesemi.com).

In phase-lock mode the lock detector asserts the LOCK signal as soon as a lock condition is determined. In fre-

quency-lock mode, however, the PLL must be in a locked condition for a set number of phase detector cycles

before the LOCK signal will be asserted. The number of cycles required before asserting the LOCK signal in fre-

quency-lock mode can be set from 16 through 256.

When the lock condition is lost the LOCK signal will be de-asserted immediately in both phase-lock and frequency-

lock detection modes. In frequency-lock mode, however, if the input reference signal is stopped, the LOCK output

may continue to be asserted. In phase-lock mode, a loss of the input reference signal will always result in de-asser-

tion of the LOCK output.

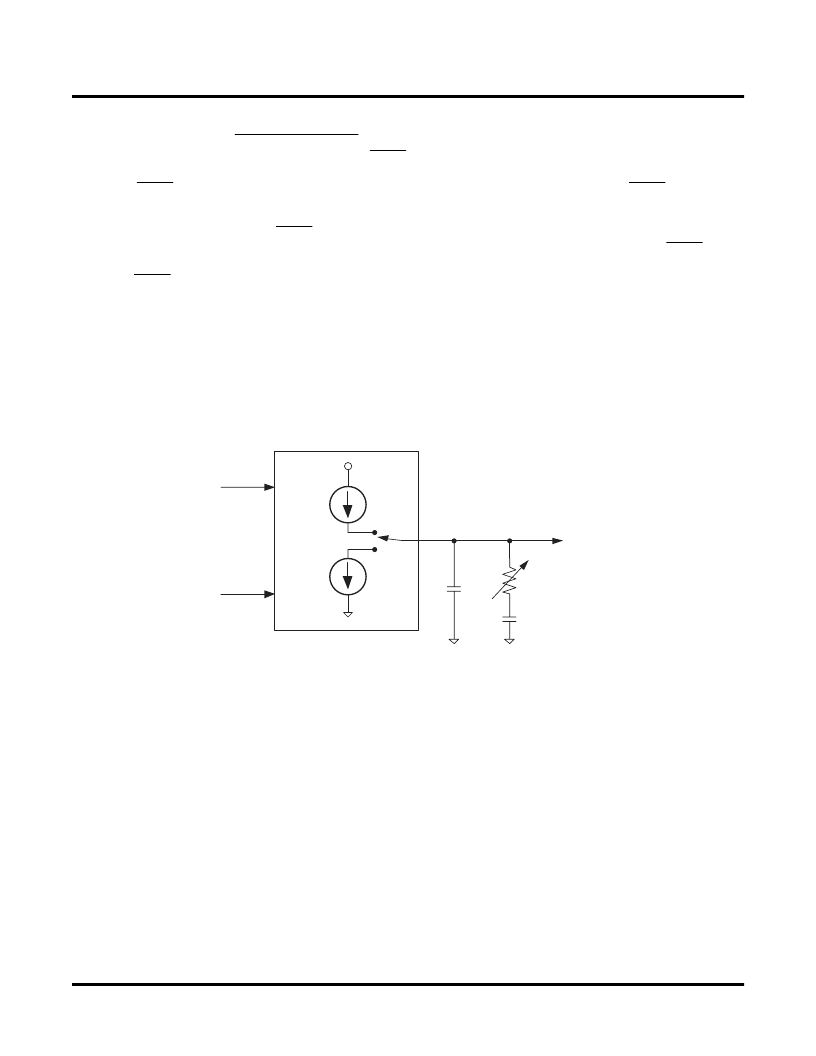

Loop Filter

A simpli

fi

ed schematic for the ispClock5600 loop

fi

lter is shown in Figure 11. The

fi

lter’s capacitors are

fi

xed, and

the response is controlled by setting the value of the phase-detector’s output current source’s and the value of the

variable resistor. The phase detector output current has 14 possible settings, ranging from 3μA to 55μA, while the

resistor may be set to any one of six values ranging from 2.3K to 9.3K. This provides a total of 84 unique I-R com-

binations which may be selected.

Figure 11. ispClock5600 Loop Filter (Simplified)

Because the selection of an optimal PLL loop

fi

lter can be a daunting task, PAC-Designer offers a set of default

fi

l-

ter settings which will provide acceptable performance for most applications. The primary criterion for selecting one

of these settings is the total division factor used in the feedback path, or the ratio between the VCO output fre-

quency and the frequency output by the N feedback divider (N x V

feedback

). Table 2 lists these default settings and

conditions under which they should be used.

To VCO

R

C

2

C

1

I

I

Phase Detector

From

M-divider

From

N-divider

相關PDF資料 |

PDF描述 |

|---|---|

| ISPCLOCK5600 | In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5610V-01T100C | In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5620V-01T100C | LED Area Light; LED Color:Blue; Leaded Process Compatible:No; Light Emitting Area:80x80mm; Peak Reflow Compatible (260 C):No; Supply Current:250mA; Supply Voltage:24VDC; Wavelength:470nm |

| ISPPAC-CLK5620V-01T100I | In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5610V-01T48C | Spot Light; LED Color:Blue; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:160mA; Supply Voltage:30VDC; Wavelength:470nm |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ISPPAC-CLK5610V-01T48C | 功能描述:時鐘驅(qū)動器及分配 3.3V 10-320MHz RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| ISPPAC-CLK5610V-01T48I | 功能描述:時鐘驅(qū)動器及分配 PROGRAMMABLE ZERO DELAY CL GEN RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| ISPPAC-CLK5610V-01TN100C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5610V-01TN100I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5610V-01TN48C | 功能描述:時鐘驅(qū)動器及分配 PROGRAMMABLE ZERO DELAY CL GEN RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。