- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384536 > ISPGDX80VA-3T100 (LATTICE SEMICONDUCTOR CORP) In-System Programmable 3.3V Generic Digital CrosspointTM PDF資料下載

參數(shù)資料

| 型號(hào): | ISPGDX80VA-3T100 |

| 廠(chǎng)商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類(lèi): | PLD |

| 英文描述: | In-System Programmable 3.3V Generic Digital CrosspointTM |

| 中文描述: | EE PLD, 3 ns, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁(yè)數(shù): | 14/27頁(yè) |

| 文件大?。?/td> | 346K |

| 代理商: | ISPGDX80VA-3T100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

14

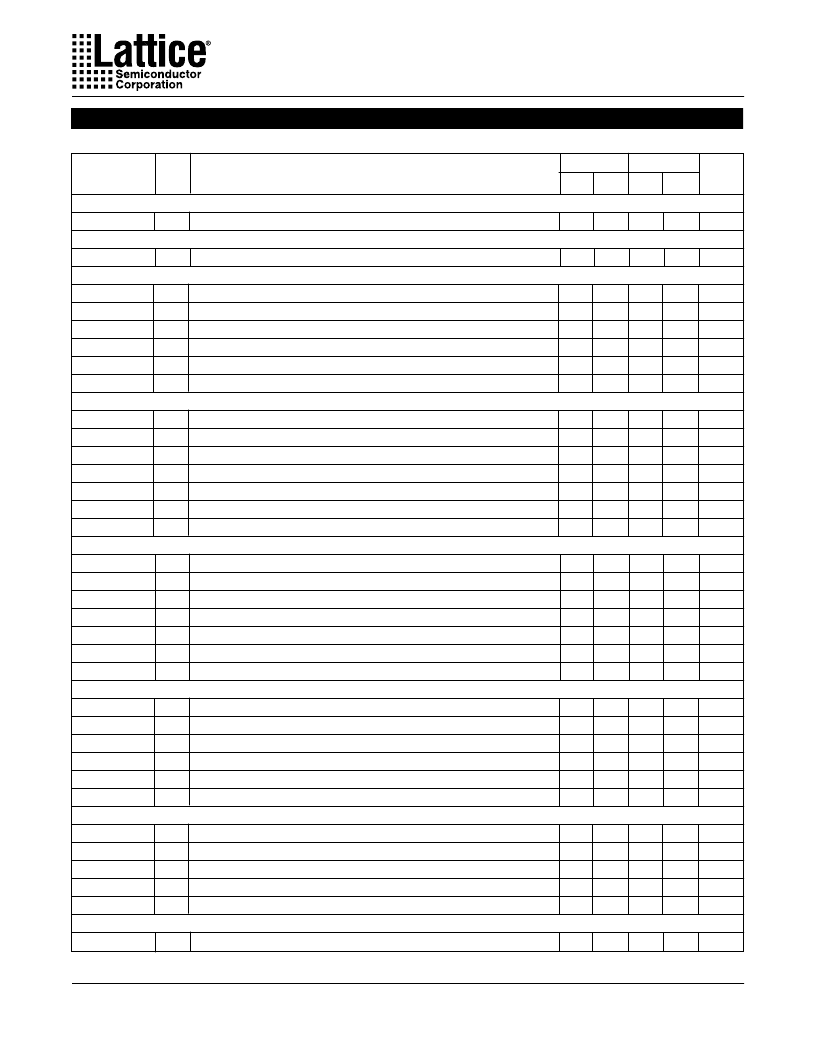

Specifications

ispGDX80VA

-3

-5

PARAMETER #

Inputs

t

io

GRP

t

grp

MUX

t

muxd

t

muxexp

t

muxs

t

muxsio

t

muxsg

t

muxselexp

Register

t

iolat

t

iosu

t

ioh

t

ioco

t

ior

t

cesu

t

ceh

Data Path

t

fdbk

t

iobp

t

ioob

t

muxcg

t

muxcio

t

iodg

t

iodio

Outputs

t

ob

t

obs

t

oeen

t

oedis

t

goe

t

toe

Clocks

t

ioclk

t

gclk

t

gclkeng

t

gclkenio

t

ioclkeng

Global Reset

t

gr

1. Internal Timing Parameters are not tested and are for reference only.

2. Refer to the Timing Model in this data sheet for further details.

DESCRIPTION

1

MIN. MAX. MIN. MAX. UNITS

32

Input Buffer Delay

—

0.4

—

0.9

ns

33

GRP Delay

—

1.1

—

1.1

ns

34

35

36

37

38

39

I/O Cell MUX A/B/C/D Data Delay

I/O Cell MUX A/B/C/D Expander Delay

I/O Cell Data Select

I/O Cell Data Select (I/O Clock)

I/O Cell Data Select (Yx Clock)

I/O Cell MUX Data Select Expander Delay

—

—

—

—

—

—

1.0

1.5

1.0

1.5

1.5

1.5

—

—

—

—

—

—

1.5

2.0

1.5

3.0

2.0

2.0

ns

ns

ns

ns

ns

ns

40

41

42

43

44

45

46

I/O Latch Delay

I/O Register Setup Time Before Clock

I/O Register Hold Time After Clock

I/O Register Clock to Output Delay

I/O Reset to Output Delay

I/O Clock Enable Setup Time Before Clock

I/O Clock Enable Hold Time After Clock

—

—

—

—

—

—

—

1.0

0.8

1.7

1.2

1.0

2.3

0.2

—

—

—

—

—

—

—

1.0

2.0

1.5

0.5

1.5

2.0

0.5

ns

ns

ns

ns

ns

ns

ns

47

48

49

50

51

52

53

I/O Register Feedback Delay

I/O Register Bypass Delay

I/O Register Output Buffer Delay

I/O Register A/B/C/D Data Input MUX Delay (Yx Clock)

I/O Register A/B/C/D Data Input MUX Delay (I/O Clock)

I/O Register I/O MUX Delay (Yx Clock)

I/O Register I/O MUX Delay (I/O Clock)

—

—

—

—

—

—

—

0.6

0.0

0.0

1.5

1.5

3.5

3.5

—

—

—

—

—

—

—

0.9

0.0

0.0

2.0

3.0

4.0

5.0

ns

ns

ns

ns

ns

ns

ns

54

55

56

57

58

59

Output Buffer Delay

Output Buffer Delay (Slow Slew Option)

I/O Cell OE to Output Enable

I/O Cell OE to Output Disable

GRP Output Enable and Disable Delay

Test OE Enable and Disable Delay

—

—

—

—

—

—

1.0

4.5

3.5

3.5

0.0

2.5

—

—

—

—

—

—

1.5

6.5

4.0

4.0

0.0

2.0

ns

ns

ns

ns

ns

ns

60

61

62

63

64

I/O Clock Delay

Global Clock Delay

Global Clock Enable (Yx Clock)

Global Clock Enable (I/O Clock)

I/O Clock Enable (Yx Clock)

—

—

—

—

—

0.3

1.3

1.5

1.0

0.5

—

—

—

—

—

2.0

2.0

2.5

3.5

2.5

ns

ns

ns

ns

ns

65

Global Reset to I/O Register Latch

—

6.0

—

11.0

ns

Internal Timing Parameters

1

Over Recommended Operating Conditions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPGDX80VA-5T100 | In-System Programmable 3.3V Generic Digital CrosspointTM |

| ISPGDX80VA-5T100I | In-System Programmable 3.3V Generic Digital CrosspointTM |

| ISPGDX80VA-7T100I | PHOTOELECTRIC PRODUCTS |

| ISPGDX80VA-9T100I | In-System Programmable 3.3V Generic Digital CrosspointTM |

| ISPL1048E-125LQI | High-Density Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPGDX80VA3T100-5I | 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPGDX80VA-3TN100 | 功能描述:模擬和數(shù)字交叉點(diǎn) IC PROGRAMMABLE GEN DIG CROSSPOINT RoHS:否 制造商:Micrel 配置:2 x 2 封裝 / 箱體:MLF-16 數(shù)據(jù)速率:10.7 Gbps 輸入電平:CML, LVDS, LVPECL 輸出電平:CML 電源電壓-最大:3.6 V 電源電壓-最小:2.375 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 產(chǎn)品:Digital Crosspoint 封裝:Tube |

| ISPGDX80VA5T100 | 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPGDX80VA-5T100 | 功能描述:模擬和數(shù)字交叉點(diǎn) IC PROGRAMMABLE GEN DIG CROSSPOINT RoHS:否 制造商:Micrel 配置:2 x 2 封裝 / 箱體:MLF-16 數(shù)據(jù)速率:10.7 Gbps 輸入電平:CML, LVDS, LVPECL 輸出電平:CML 電源電壓-最大:3.6 V 電源電壓-最小:2.375 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 產(chǎn)品:Digital Crosspoint 封裝:Tube |

| ISPGDX80VA-5T100I | 功能描述:模擬和數(shù)字交叉點(diǎn) IC PROGRAMMABLE GEN DIG CROSSPOINT RoHS:否 制造商:Micrel 配置:2 x 2 封裝 / 箱體:MLF-16 數(shù)據(jù)速率:10.7 Gbps 輸入電平:CML, LVDS, LVPECL 輸出電平:CML 電源電壓-最大:3.6 V 電源電壓-最小:2.375 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 產(chǎn)品:Digital Crosspoint 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。