- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383133 > ISL5216KI (INTERSIL CORP) Four-Channel Programmable Digital DownConverter PDF資料下載

參數(shù)資料

| 型號(hào): | ISL5216KI |

| 廠商: | INTERSIL CORP |

| 元件分類(lèi): | 無(wú)繩電話/電話 |

| 英文描述: | Four-Channel Programmable Digital DownConverter |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PBGA196 |

| 封裝: | 12 X 12 MM, 0.80 MM PITCH, PLASTIC, BGA-196 |

| 文件頁(yè)數(shù): | 20/65頁(yè) |

| 文件大小: | 1384K |

| 代理商: | ISL5216KI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)

20

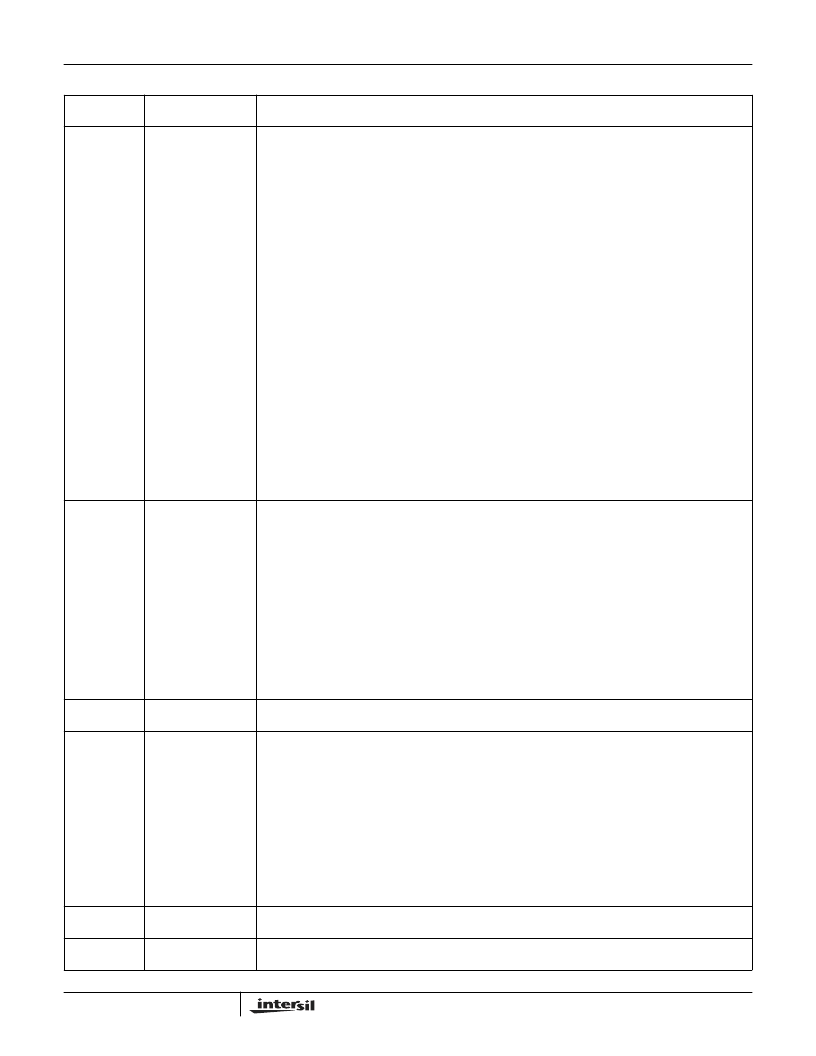

28:18

Destination

Destination Field Bit Mapping

28

27

26

25

24

23

22

21

20

19

18

AGCLFGN AGCLF

Path1

Path0

OS

FB

F4

F3

F2

F1

F0

AGCLFGN AGC loop gain select. Only applies to Path 1.

Loop gain 0 or 1 if AGCLF bit is set. Set to 0 (1 is a test mode for future chips).

AGCLF

AGC loop

fi

lter enable. Only applies to Path 1. The AGC loop is updated with the magnitude

of this sample (Path(1:0) = 01).

Path(1:0)

Back End Data Routing Path Selection. (see Back End Data Routing

fi

gure)

00

Route output back to

fi

lter compute engine input to another FIR in the

fi

lter chain.

01

Route output thru the FIFO and AGC to outputs I1 and Q1.

10

Route output to I2 and Q2, bypassing the FIFO and AGC. This path

also routes to next channel FIR input.

11

Route output thru the FIFO and AGC to outputs I2 and Q2.

OS

Enable output strobe. Setting this bit generates a data ready signal when the data reaches

the output section and starts the serial output sequence (paths 1, 2, 3). If OS is not set,

there will be no output to the outside world from this channel, for that output calculation, but

the data will be loaded into its output holding register (OS would not be set when routing the

data to another back end when cascading channels).

FB

Feedback data path. When set, the magnitude and dphi/dt from the cartesian-to-polar coor-

dinate converter block are routed to the

fi

lter compute engine input (magnitude goes to the

I input and dphi/dt goes to the Q input). Provided for discriminator

fi

ltering.

F(4:0)

Filter select. For data recirculated to the input of the FIR processor by path 0 or from the

cartesian to polar coordinate converter output, these bits tell which

fi

lter sequencer step

gets it as an input.

31:29

Round Select

31:29

Round Select (Add rounding bit at speci

fi

ed location).

000

2

-24

, use this code when downshifting is not used.

001

2

-23

010

2

-22

011

2

-21

100

2

-20

101

2

-19

110

2

-18

111

no rounding.

Provided for use with the coef

fi

cient down-shift bits.

41:32

Data Memory

Block Start

Memory block base address, 0-1023, 0-383 are valid for the ISL5216.

44:42

Data Memory

Block Size

44:42

Block Size.

0

8

1

16

2

32

3

64

4

128

5

256

6

512

7

(modulo addressing is used).

1024

52:45

Data Memory

Block-to-Block Step

0-255, usually equal to the decimation factor for the FIR in this instruction.

62:53

Coefficient Memory

Block Start

Memory base address of coefficients, 0-1023, 0-511 are valid on the ISL5216.

INSTRUCTION BIT FIELDS (Continued)

BIT

POSITIONS

FUNCTION

DESCRIPTION

ISL5216

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISL5216 | Four-Channel Programmable Digital DownConverter |

| ISL5217EVAL1 | Quad Programmable Up Converter |

| ISL5217KI | Quad Programmable Up Converter |

| ISL5217 | Quad Programmable Up Converter |

| ISL5217KIZ | Quad Programmable Up Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISL5216KI-1 | 功能描述:上下轉(zhuǎn)換器 QUAD DIGITAL DOWNCONVERTER,IND TEMP,1.OMM PITCH BGA PACKAG RoHS:否 制造商:Texas Instruments 產(chǎn)品:Down Converters 射頻:52 MHz to 78 MHz 中頻:300 MHz LO頻率: 功率增益: P1dB: 工作電源電壓:1.8 V, 3.3 V 工作電源電流:120 mA 最大功率耗散:1 W 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PQFP-128 |

| ISL5216KI-1Z | 功能描述:上下轉(zhuǎn)換器 W/ANL QD DIG DWNCNVRTR 1 OM PITCH RoHS:否 制造商:Texas Instruments 產(chǎn)品:Down Converters 射頻:52 MHz to 78 MHz 中頻:300 MHz LO頻率: 功率增益: P1dB: 工作電源電壓:1.8 V, 3.3 V 工作電源電流:120 mA 最大功率耗散:1 W 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PQFP-128 |

| ISL5216KIZ | 功能描述:上下轉(zhuǎn)換器 W/ANNEAL QD DIGTL DWNCNVRTR IND TEMP RoHS:否 制造商:Texas Instruments 產(chǎn)品:Down Converters 射頻:52 MHz to 78 MHz 中頻:300 MHz LO頻率: 功率增益: P1dB: 工作電源電壓:1.8 V, 3.3 V 工作電源電流:120 mA 最大功率耗散:1 W 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PQFP-128 |

| ISL5217 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Quad Programmable Up Converter |

| ISL5217_05 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Quad Programmable Up Converter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。