- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384484 > INT5130 (Electronic Theatre Controls, Inc.) Integrated Powerline MAC/PHY Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | INT5130 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Integrated Powerline MAC/PHY Transceiver |

| 中文描述: | 綜合電力線MAC /物理層收發(fā)器 |

| 文件頁數(shù): | 2/38頁 |

| 文件大?。?/td> | 1352K |

| 代理商: | INT5130 |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

INTELLON CONFIDENTIAL

Rev 8.1

2

ADVANCE INFORMATION

INT5130 Integrated Powerline MAC /PHY Transceiver Technical Data Sheet

The INT5130 implements Intellon’s patented PowerPacket OFDM technology and is fully compliant with the

HomePlug Powerline Alliance

Industry Specification v1.0

. Specifically tailored to reliably deliver up to 14

Mbps over the difficult powerline communication environment, the INT5130 combats deep attenuation notches,

noises sources, and multi-path fading by allocating usable frequencies according to the signal to noise ratio

(SNR). Synchronization is achieved in low SNR channels without the use of pilot carriers. The MAC

implements a CSMA/CA scheme with prioritization and automatic repeat request (ARQ) for reliable delivery of

Ethernet packets via packet encapsulation. Built-in quality-of-service (QoS) features provide the necessary

bandwidth for multimedia payloads including voice, data, audio, and video. Prioritized random access along with

segment bursting minimizes the demands on the receiver resources and maximizes the throughput of the

network while still providing excellent latency response and jitter performance. The INT5130’s contention-free

access capability extends this concept of segment bursting to allow the transmission of multiple frames over

the powerline without relinquishing the control of the medium. Utilizing contention-free access, a single station

may act as a controller for the entire network.

System designers have the option of embedding PowerPacket-specific control information within the packet

stream for optimal control and performance or may choose to provide this information via the separate

E

2

PROM interface. Providing this configuration and control information through a separate E

2

PROM interface

allows the system designer to leverage standard Ethernet drivers.

The INT5130 operates on both 2.5V and 3.3V supplies, offers 5V I/O tolerance, and is packaged in a 144-pin

LQFP. Intellon offers a complete solution for powerline communication applications by providing the INT5130 in

conjunction with the INT1000 Analog Conversion IC.

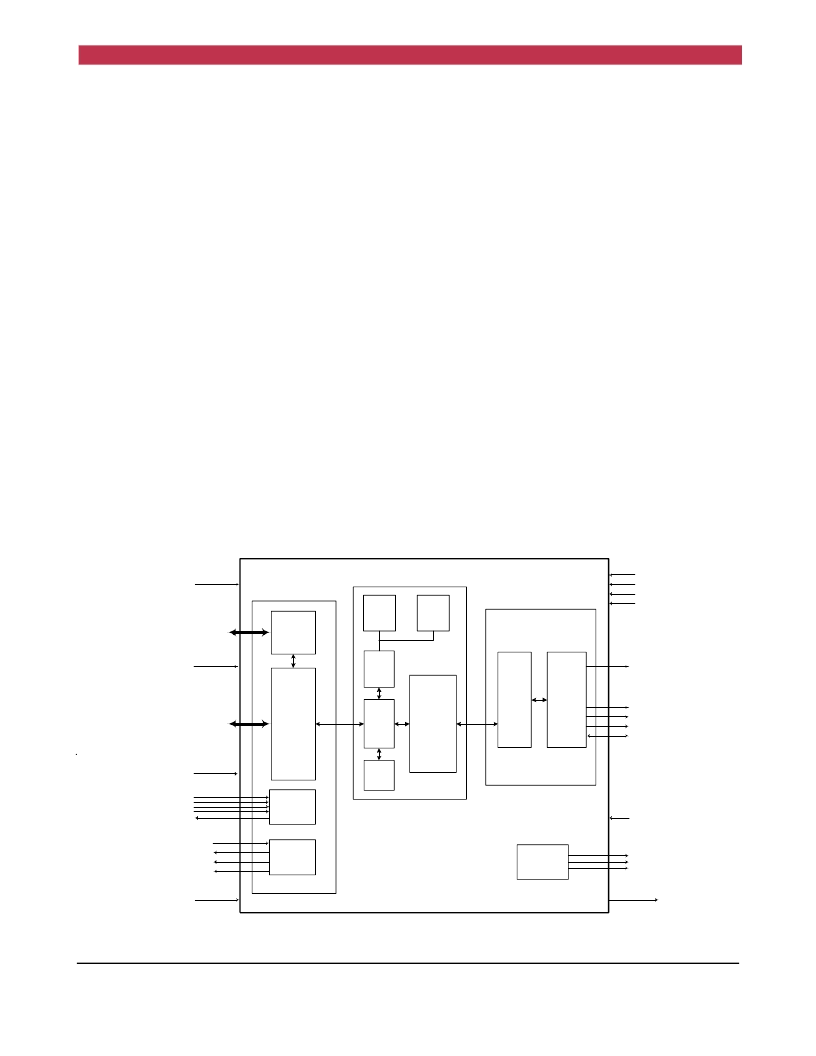

Functional Block Diagram

TX[3:0],TXCLK,TXEN,TX_ER

COL,CRS

- OR -

RXD,RXCLK,RXEN

TXD,TXCLK,TXEN

COL,TXBSY

PHY

Core

PowerPacket MAC

PowerPacket PHY

INT5130

Interface Block

MII/GPSI

Interface

DMA

&

Link

Sequencer

RISC

uProc

Core

ROM

RAM

Arbiter

Buffer

RAM

AFE

Interface

JTAG

Port

LED

Control

CLK OUT

CLK IN

RESET

Config

Regs

MDCLK/MDIO

- OR -

SPI Control

SDI,SDO,SCLK,CS

E

2

PROM

Control

Configuration

EEPROM

Control

JTAG

Control

MII/GPSI

Select

MII

MDI/SPI

Select

MDIO Control

Power

&

GND

ADC

DAC

IFace

Gain

Control

MDIO

Address

Select

LEDs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| INT5130CS | Integrated Powerline MAC/PHY Transceiver |

| INTENSI-FI | DRAFT-802.11n PRODUCT FAMILY |

| IP1001 | Full Function Synchronous Buck Power Block |

| IP1202 | Dual Output Full Function 2 Phase Synchronous Buck Power Block Integrated Power Semiconductors, PWM Control & Passives |

| IP2002 | Synchronous Buck Synchronous Buck Integrated Power Semiconductors, Drivers & Passives |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| INT5130CS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Integrated Powerline MAC/PHY Transceiver |

| INT5200A0TR | 制造商:INTELLON 功能描述: |

| INT57P7089 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:IBM 功能描述: |

| INT57P7090 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:IBM 功能描述: |

| INT57P7091 | 制造商:IBM 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。