- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384484 > INT5130 (Electronic Theatre Controls, Inc.) Integrated Powerline MAC/PHY Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | INT5130 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Integrated Powerline MAC/PHY Transceiver |

| 中文描述: | 綜合電力線MAC /物理層收發(fā)器 |

| 文件頁(yè)數(shù): | 19/38頁(yè) |

| 文件大?。?/td> | 1352K |

| 代理商: | INT5130 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)

INTELLON CONFIDENTIAL

Rev 8.1

19

ADVANCE INFORMATION

INT5130 Integrated Powerline MAC /PHY Transceiver Technical Data Sheet

accessed from the SPI Slave port when the MDI_SPIS_N select line has been tied low to select the SPI

Slave port.

PLCSR

Register Name

MII Mandated

0

1

Control Register

Status Register

X

X

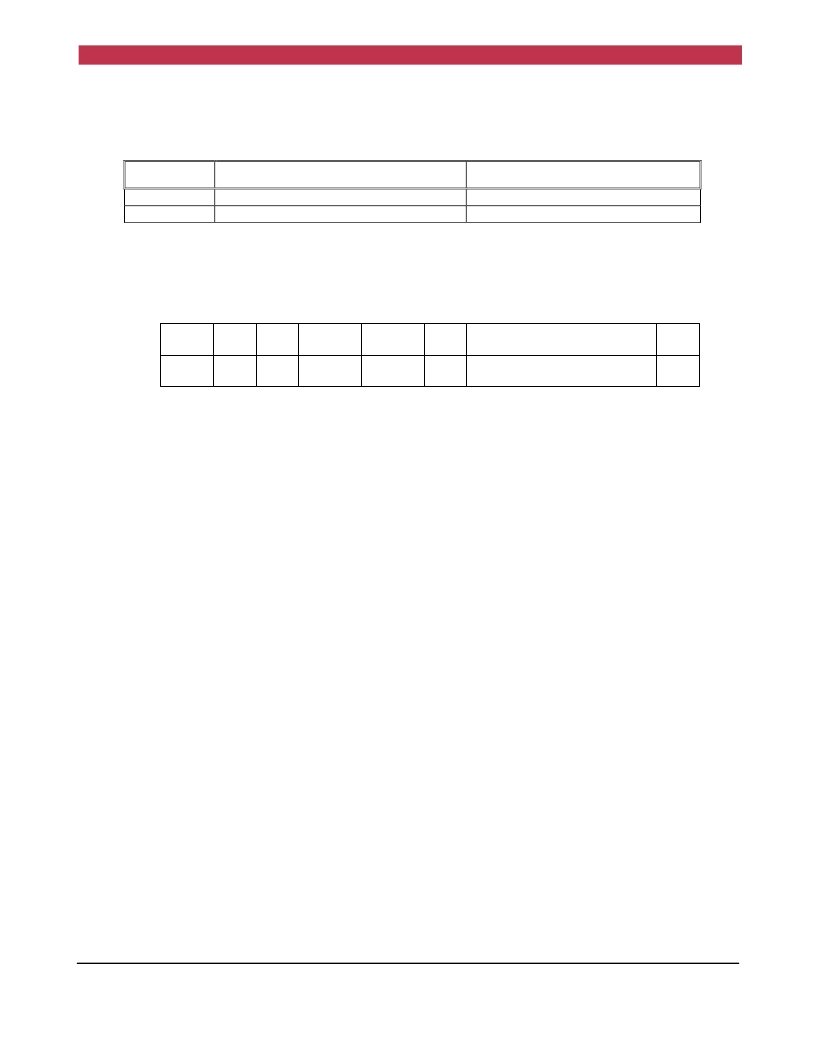

Table 5: Powerline Control and Status Register (PLCSR) Summary

Figure 13: MDI Frame Structure

PRE (Preamble)

At the beginning of each MDI transaction, the external host shall send a sequence of 32 contiguous

logic “1” bits on the MDIO signal so the INT5130 can establish synchronization. The INT5130

needs to observe this 32 bit sequence on the MII_MDIO signal before it responds to any

transaction.

ST (Start of Frame)

Indicated by a “01” pattern.

OP (Operation Code)

“10” indicates a READ. “01” indicates a WRITE.

PHYAD (PHY Address)

The PHY Address is 5 bits, allowing up the 32 unique PHY addresses. The INT5130 will respond to

PHY addresses indicated by 0bXX000. The “XX” bits of the PHY address are controlled by the

INT5130 interface pins MDI_ADRSEL(0:1). This allows the designer to assign the INT5130 to one

of 4 unique PHY addresses.

REGAD (Register Address)

The Register Address is 5 bits and is used to index the maximum of 32 individual registers in the

MDI address space. The INT5130 only implements the two mandated MII registers. 0b00000 will

index the MII Control Register and 0b00001 will index the MII Status Register.

TA (Turnaround)

The turnaround time is a 2 bit time spacing between the Register Address field and the Data field to

avoid contention during a read transaction.

For reads, both the external host and the INT5130 will remain in tri-state for the first bit time. The

INT5130 will drive a “0” during the second bit time.

DDDDDDDDDDDDDDDD

RRRRR

Data

Idle

Z

TA

Z0

PRE

REGAD

AAAAA

PHYAD

01

OP

ST

10

1...1

DDDDDDDDDDDDDDDD

RRRRR

Z

10

AAAAA

01

01

1...1

READ

WRITE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| INT5130CS | Integrated Powerline MAC/PHY Transceiver |

| INTENSI-FI | DRAFT-802.11n PRODUCT FAMILY |

| IP1001 | Full Function Synchronous Buck Power Block |

| IP1202 | Dual Output Full Function 2 Phase Synchronous Buck Power Block Integrated Power Semiconductors, PWM Control & Passives |

| IP2002 | Synchronous Buck Synchronous Buck Integrated Power Semiconductors, Drivers & Passives |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| INT5130CS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Integrated Powerline MAC/PHY Transceiver |

| INT5200A0TR | 制造商:INTELLON 功能描述: |

| INT57P7089 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:IBM 功能描述: |

| INT57P7090 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:IBM 功能描述: |

| INT57P7091 | 制造商:IBM 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。