- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370740 > HY5R288HC -|2.5V|8K|40|Direct RDRAM - 288M PDF資料下載

參數(shù)資料

| 型號: | HY5R288HC |

| 英文描述: | -|2.5V|8K|40|Direct RDRAM - 288M |

| 中文描述: | - |為2.5V | 8K的| 40 |直接RDRAM的- 288M |

| 文件頁數(shù): | 53/64頁 |

| 文件大?。?/td> | 4542K |

| 代理商: | HY5R288HC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Rev.0.9 / Dec.2000

53

Direct RDRAM

256/288-Mbit (512Kx16/18x32s) Preliminary

RSL - Transmit Timing

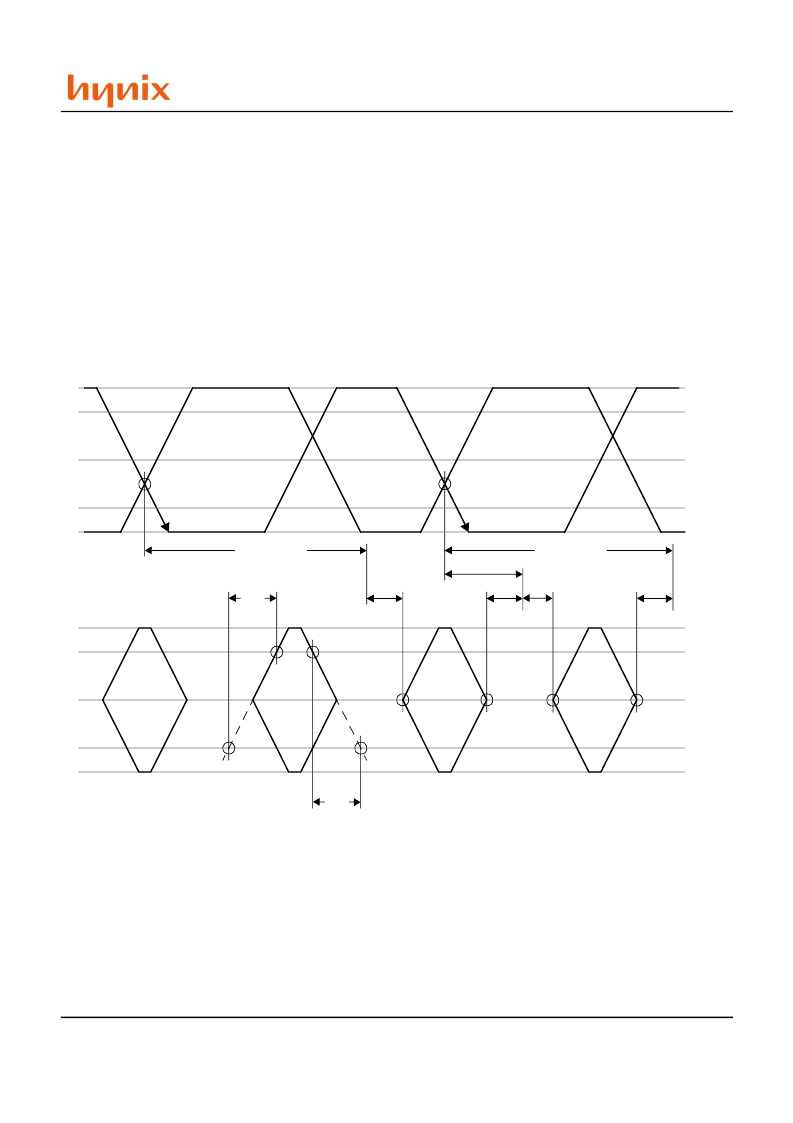

Figure 56: is a timing diagram which shows the detailed

requirements for the RSL output signals on the Channel.

The DQA and DQB signals are outputs to transmit informa-

tion that is received by a Direct RAC on the Channel. Each

signal is driven twice per t

CYCLE

interval. The beginning

and end of the even transmit window is at the 75% point of

the previous cycle and at the 25% point of the current cycle.

The beginning and end of the odd transmit window is at the

25% point and at the 75% point of the current cycle. These

transmit points are measured relative to the crossing points

of the falling CTM clock edge. The size of the actual

transmit window is less than the ideal t

CYCLE

/2, as indicated

by the non-zero values of t

Q,MIN

and t

Q,MAX

. The t

Q

param-

eters are measured at the V

REF

voltage point of the output

transition.

The t

QR

and t

QF

rise- and fall-time parameters are measured

at the 20% and 80% points of the output transition.

Figure 56: RSL Timing - Data Signals for Transmit

t

Q,MIN

t

Q,MAX

t

Q,MAX

t

Q,MIN

0.25t

CYCLE

V

QH

V

REF

V

QL

80%

20%

V

CIH

50%

V

CIL

80%

20%

CTM

CTMN

t

QF

t

QR

even

odd

0.75t

CYCLE

0.75t

CYCLE

DQA

DQB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5V16CF | 1Mx16|3.3V|4K|H|SDR SDRAM - 16M |

| HY5V16CF-H | x16 SDRAM |

| HY5V16CF-S | x16 SDRAM |

| HY6116-10 | x8 SRAM |

| HY6116-12 | x8 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5S2B6DLF-BE | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLFP-BE | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLFP-SE | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S2B6DLF-SE | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:4Banks x 2M x 16bits Synchronous DRAM |

| HY5S5B2BLF-6E | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256M (8Mx32bit) Mobile SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。