- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370727 > HV7131D-COF (HYNIX SEMICONDUCTOR INC) CMOS IMAGE SENSOR With 8-bit ADC PDF資料下載

參數(shù)資料

| 型號: | HV7131D-COF |

| 廠商: | HYNIX SEMICONDUCTOR INC |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | CMOS IMAGE SENSOR With 8-bit ADC |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, DSS24 |

| 封裝: | COF-24 |

| 文件頁數(shù): | 19/61頁 |

| 文件大小: | 2621K |

| 代理商: | HV7131D-COF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

HV7131GP

2004/10/29 V2.4 19

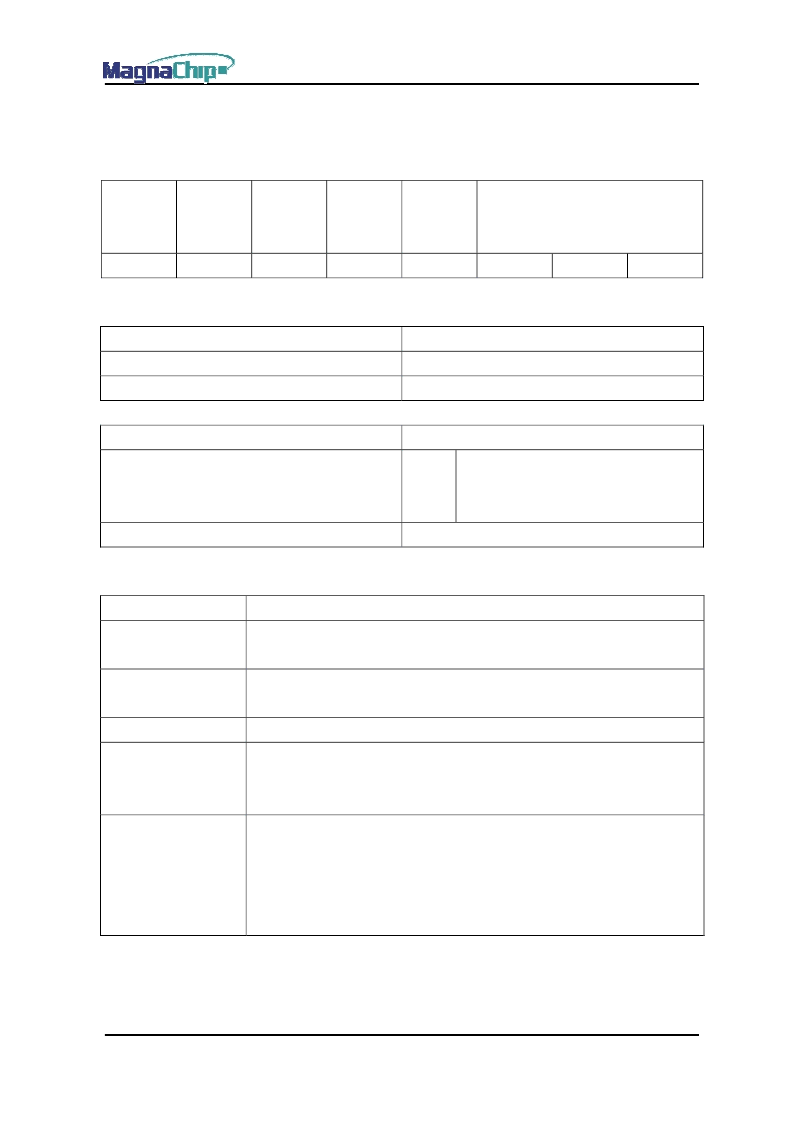

Sensor Control B [SCTRB : 02h : 00h]

7

6

5

4

3

2

1

0

AE/AWB

Block

Sleep

Datapath

Block

Sleep

Analog

Block

Sleep

Sleep

Mode

Strobe

Enable

Clock Division

0

0

0

0

0

0

0

0

< Clock Acronym Definition >

MCF : Master Clock Frequency

DCF : Divided Clock Frequency

SCF : Sensor Clock Frequency

ICF : Image Processing Clock Frequency

VCF : Video Clock Frequency

LCF : Line Clock Frequency

< Clock Frequency Relation >

MCF : MCF

DCF : MCF/Clock Division

SCF : DCF/2

ICF

SCF for 3x3 interpolation,

SCF/2 for 1/4 subsampling mode

SCF/4 for 1/16 subsampling mode

VCF : ICF for 16bit output, ICF*2 for 8bit output

LCF : 1/(HBLANK Period + HSYNC Period)

AE/AWB Block Sleep

AE/AWB block goes into sleep mode with this bit set to high.

Datapath Block Sleep

Image processing datapath block goes into sleep mode with this bit set to

high.

Analog Block Sleep

all internal analog block goes into sleep mode with this bit set to high. With

All Digital Block Sleep active, sensor goes into power down mode.

Sleep Mode

all internal digital and analog block goes into sleep with this bit set to high.

Strobe Enable

When strobe signal is enabled by this bit, STROBE pin will indicates when

strobe light should be splashed in the dark environment to get adequate

lighted image.

Clock Division

divides input master clock(IMC) for internal use. Internal divided clock

frequency(DCF) is defined as master clock frequency(MCF) divided by

specified clock divisor. Internal divided clock frequency(DCF) is as follows.

000 : MCF, 001 : MCF/2, 010 : MCF/4, 011 : MCF/8

100 : MCF/16, 101 : MCF/32, 110 : MCF/64, 111 : MCF/128

Sensor Control C [SCTRC : 03h : 01h]

相關PDF資料 |

PDF描述 |

|---|---|

| HV7131R | CMOS Image Sensor |

| HVB14S | TIP REPLACEMNT TEFLON FOR DP-100 |

| HVB190S | |

| HVB27WK | TIP REPLACEMNT TEFLON FOR DP-200 |

| HVB350BYP | |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HV7131E1 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:CMOS IMAGE SENSOR With 8-bit ADC |

| HV7131GP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Image Sensor with Image Signal Processing |

| HV7131R | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Image Sensor |

| HV7131RP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Image Sensor with Image Signal Processing |

| HV7141 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:CMOS IMAGE SENSOR With 8-bit ADC |

發(fā)布緊急采購,3分鐘左右您將得到回復。