- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1024 Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) PDF資料下載

參數(shù)資料

| 型號(hào): | HDMP-1024 |

| 英文描述: | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) |

| 中文描述: | 低成本千兆速率接收芯片組配備TTL的I / O(帶的TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) |

| 文件頁(yè)數(shù): | 39/40頁(yè) |

| 文件大小: | 363K |

| 代理商: | HDMP-1024 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)當(dāng)前第39頁(yè)第40頁(yè)

39

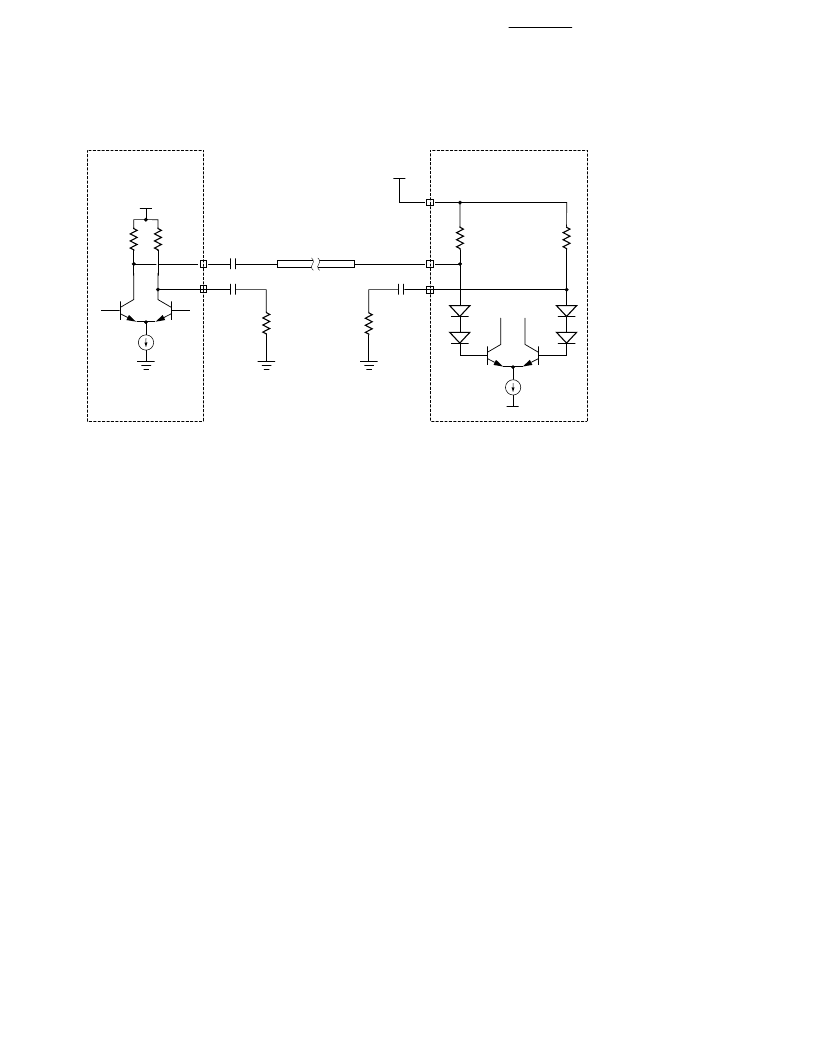

Figure 22. I-H50 and O-BLL Simplified Circuit Schematic.

Mode Options

G-Link has several option pins

which set the modes of operation.

Common to both the Tx and the

Rx are M20SEL, DIV0, and DIV1,

FLAGSEL, and LOOPEN. Local to

the Tx are MDFSEL, EHCLKSEL,

and HCLKON. Local to the Rx are

EQEN and TCLKSEL. These pins

are all I-TTL, and can be set as

described below.

M20SEL sets the width of the

frame to 16/20 bits.

DIV1 / DIV0 sets the frequency

bands of operation. Refer to the

Setting the Operating Data Rate

Range

section for frequency band

selection. It is recommended that

applications near the ends of the

bands have jumpers for DIV0 and

DIV1 inputs, so that the board can

accommodate possible lot-to-lot

band variations over the life of the

board design.

FLAGSEL selects whether the flag

bit is reserved for error detection

by the link, or used as an extra bit

available for the user.

LOOPEN selects whether the

normal data (DIN/ DIN*) or the

loop back data (LIN/ LIN*) are

used.

MDFSEL selects the Tx single or

double frame modes.

ECHKSEL selects whether to lock

onto a frame-rate clock at

STRBIN or to use this clock as the

high speed clock and bypass the

PLL in the Tx. This input is used

mainly for testing, and should be

normally set low.

HCLKON turns on the high speed

serial clock outputs of the Tx.

This option was added to

conserve power.

EQEN disables or enables the

data equalizer in the Rx for cable

applications.

TCLKSEL selects the clock source

from either the serial data stream

or from the TCLK inputs for the

Rx. This input is for testing only,

and should normally be set low.

Z

o

= 50

V

EE

28 mA

80

80

50

50

50

V

CC

O-BLL

I-H50

0.1 μF

50

V

CC_HS

0.1 μF

0.1 μF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

| HDMP-1514 | Fibre Channel Receiver Chipset(光纖通道接收芯片) |

| HDMP-1526 | Transistor Diode Kit;Contents Of Kit:Transistor/Diode Kit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034A | 制造商:HP 制造商全稱:Agilent(Hewlett-Packard) 功能描述:Transmitter/Receiver Chip Set |

| HDMP-1512 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fibre Channel Transmitter and Receiver Chipset |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。