- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1014 Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 PDF資料下載

參數(shù)資料

| 型號: | HDMP-1014 |

| 英文描述: | Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 |

| 中文描述: | 4Low成本千兆速率發(fā)送/接收芯片組 |

| 文件頁數(shù): | 10/42頁 |

| 文件大小: | 321K |

| 代理商: | HDMP-1014 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

582

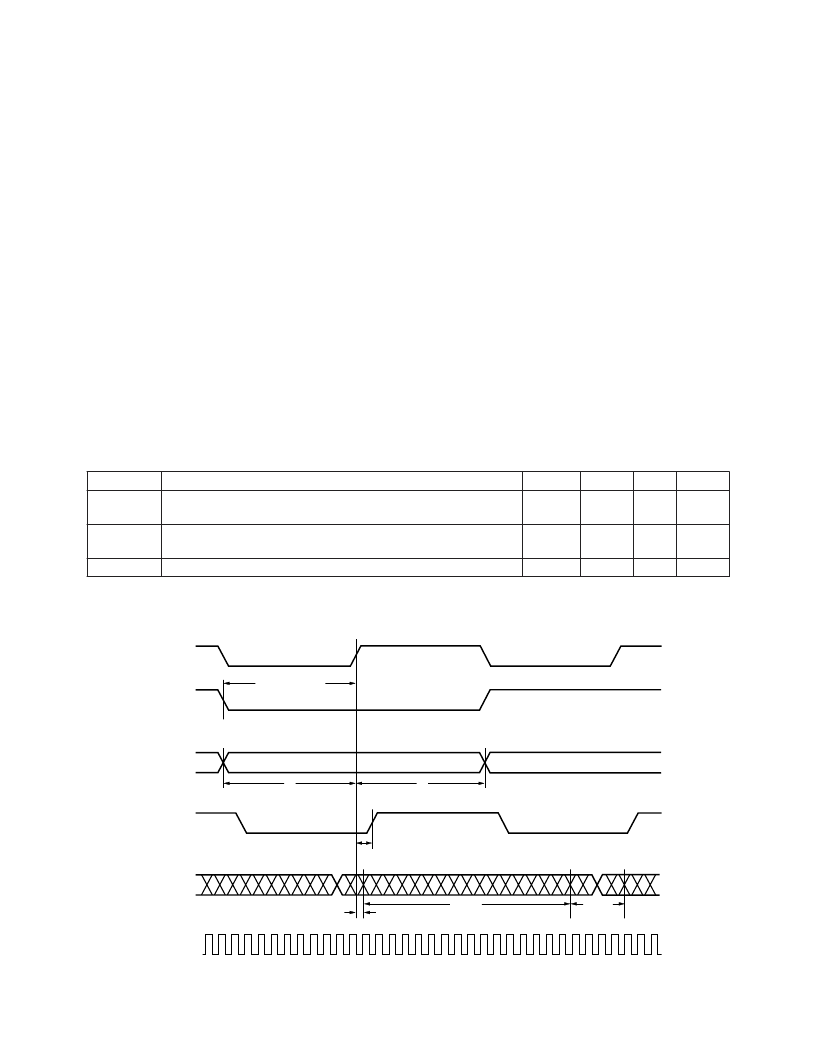

HDMP-1012 (Tx) Timing

Figure 6 shows the Tx timing

diagram. Under normal

operations, the Tx PLL locks an

internally generated clock to the

incoming STRBIN. The incoming

data, D0-D19, ED, FF, DAV*,

CAV*, and FLAG, are latched by

this internal clock. For

MDFSEL=0, the input rate of

STRBIN is expected to be the

same as the parallel data rate. For

MDFSEL=1, STRBIN should be 1/

2 of the incoming parallel data

rate. The data must be valid

before it’s sampled for the set-up

time (t

s

), and remain valid after

it’s sampled for the hold time (t

h

).

The set-up and hold times are

referenced to STRBIN. This

reference is the positive edge of

STRBIN for MDFSEL=0, and is 1/

2 the frame period from the

positive or negative edge of

STRBIN for MDFSEL=1.

STRBOUT appears after this

reference with a delay of T

strb

.

The rate of STRBOUT is always

the same as the word rate of the

incoming data, independent of

MDFSEL.

The start of a frame, D0, in the

high speed serial output occurs

after a delay of td after the rising

edge of the STRBIN. The typical

value of td may be calculated by

using the following formula:

td = ( 2 * serial bit duration -

0.5 ns) ns

Figure 6. HDMP-1012 (Tx) Timing Diagram.

HDMP-1012 (Tx) Timing Characteristics

Tc = 0

°

C to +85

°

C, V

EE

= -4.5 V to -5.5 V

Symbol

t

s

Setup Time, for Rising Edge of STRBIN Relative to

D0-D19, ED, FF, DAV*, CAV* and FLAG

t

h

Hold Time, for Rising Edge of STRBIN Relative to

D0-D19, ED, FF, DAV*, CAV* and FLAG

T

strb

STRBOUT - STRBIN Delay

Parameter

Units

nsec

Min.

6

Typ.

Max.

nsec

0

nsec

1.5

3

1/2 FRAME PERIOD

t

s

t

h

t

strb

t

d

D-FIELD

C-FIELD

STRBIN

MDFSEL = 0

STRBIN

MDFSEL = 1

D00 - D19

ED, FF

DAV*, CAV*

FLAG

STRBOUT

DOUT

HCLK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1022 | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) |

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1022 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1024 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。