- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295495 > DDC112U/1K (TEXAS INSTRUMENTS INC) 2-CH 20-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO28 PDF資料下載

參數(shù)資料

| 型號: | DDC112U/1K |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 2-CH 20-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO28 |

| 封裝: | GREEN, PLASTIC, SOIC-28 |

| 文件頁數(shù): | 4/34頁 |

| 文件大小: | 776K |

| 代理商: | DDC112U/1K |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

DDC112

12

SBAS085B

www.ti.com

CLK = 10MHz

CLK = 15MHz

SYMBOL

DESCRIPTION

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

t1

Setup Time for Test Mode Enable

100

ns

t2

Setup Time for Test Mode Disable

100

ns

t3

Hold Time for Test Mode Enable

100

ns

t4

From Rising Edge of TEST to the Edge of CONV

5.4

3.6

s

while Test Mode Enabled

t5

Rising Edge to Rising Edge of TEST

5.4

3.6

s

A low-pass filter to reduce noise connects it to an opera-

tional amplifier configured as a buffer. This amplifier should

have a unity-gain bandwidth greater than 4MHz, low noise,

and input/output common-mode ranges that support VREF.

Following the buffer are capacitors placed close to the

DDC112 VREF pin. Even though the circuit in Figure 6 might

appear to be unstable due to the large output capacitors, it

works well for most operational amplifiers. It is NOT recom-

mended that series resistance be placed in the output lead

to improve stability since this can cause droop in VREF which

produces large offsets.

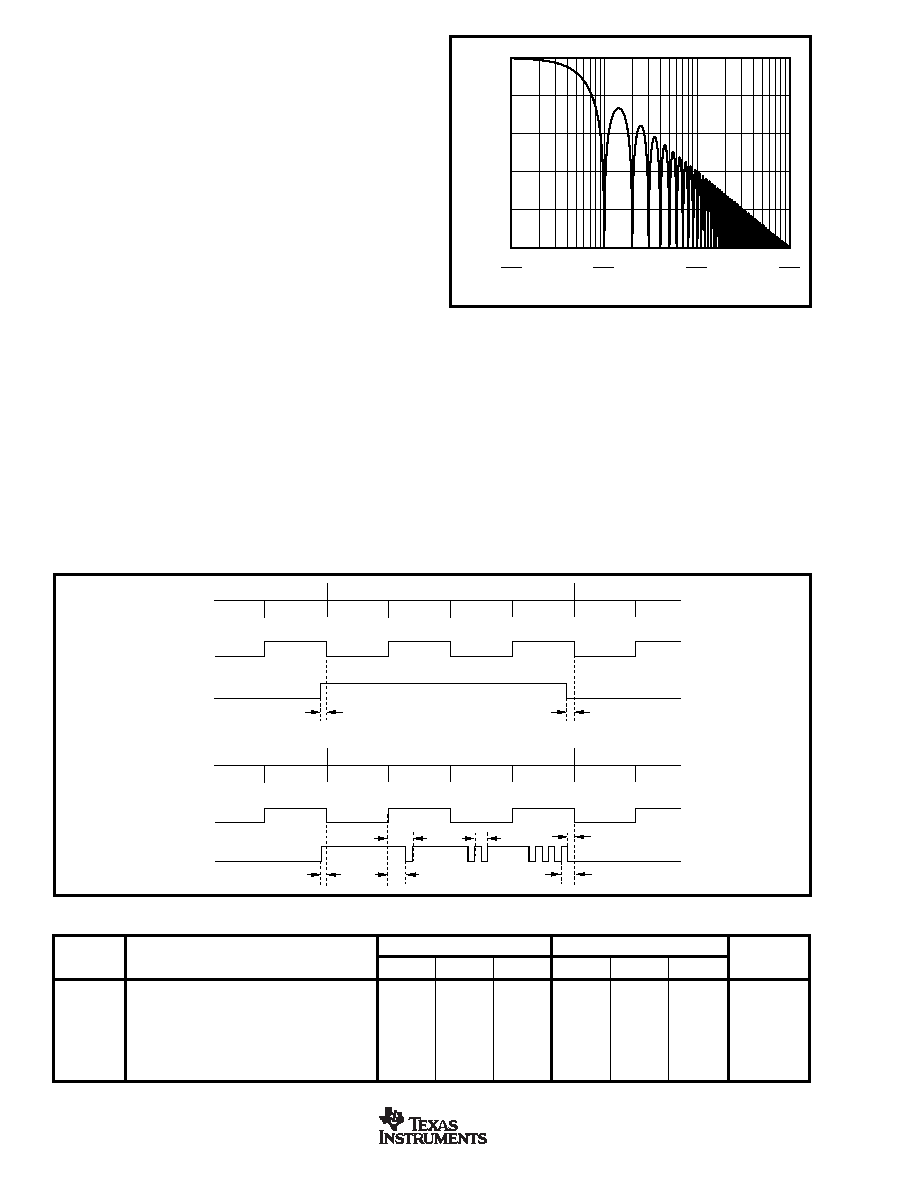

DDC112 Frequency Response

The frequency response of the DDC112 is set by the front end

integrators and is that of a traditional continuous time integra-

tor, as shown in Figure 7. By adjusting TINT, the user can

change the 3dB bandwidth and the location of the notches in

the response. The frequency response of the

Σ converter that

follows the front end integrator is of no consequence because

the converter samples a held signal from the integrators. That

is, the input to the

Σ converter is always a DC signal. Since

the output of the front end integrators are sampled, aliasing can

occur. Whenever the frequency of the input signal exceeds

one-half of the sampling rate, the signal will

fold back down to

lower frequencies.

Test Mode

When TEST is used, pins IN1 and IN2 are grounded and

packets of approximately 13pC charge are transferred to the

FIGURE 8. Timing Diagram of the Test Mode of the DDC112.

TABLE III. Timing for the DDC112 in the Test Mode.

integration capacitors of both Input 1 and Input 2. This fixed

charge can be transferred to the integration capacitors either

once during an integration cycle or multiple times. In the case

where multiple packets are transferred during one integration

period, the 13pC charge is additive. This mode can be used

in both the continuous and noncontinuous mode timing. The

timing diagrams for test mode are shown in Figure 8. The top

three lines in Figure 8 define the timing when one packet of

13pC is sent to the integration capacitors. The bottom three

lines define the timing when multiple packets are sent to the

integration capacitors.

FIGURE 7. Frequency Response of the DDC112.

0

–10

–20

–30

–40

–50

0.1

T

INT

100

T

INT

1

T

INT

10

T

INT

Frequency

Gain

(dB)

t

1

t

1

t

3

t

4

t

4

t

5

t

2

Integrate B

Action

CONV

TEST

Action

CONV

TEST

Integrate A

Test Mode Disabled

13pC into B

13pC into A

13pC into B

13pC into A

Test Mode Disabled

Test Mode Enabled

Integrate B

Integrate A

Integrate B

Integrate A

Test Mode Disabled

13pC into B

26pC into A

39pC into B

52pC into A

Test Mode Disabled

Test Mode Enabled

Integrate B

Integrate A

t

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DDC123JK-7-F | 100 mA, 50 V, 2 CHANNEL, NPN, Si, SMALL SIGNAL TRANSISTOR |

| DDL24W700G30LF | 24 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, SOLDER, SOCKET |

| DDV36W443G40LF | 36 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, SOLDER, SOCKET |

| DDV47W143G30LF | 47 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, SOLDER, SOCKET |

| DDV47W143H40LF | 47 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, SOLDER, SOCKET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DDC112UG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Dual Current Input 20-Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| DDC112UK | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Dual Current Input 20-Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| DDC112UK | 制造商:Texas Instruments 功能描述:DUAL CURRENT INPUT 20 BIT ANALOG/DIGITAL |

| DDC112UK | 制造商:Texas Instruments 功能描述:20BIT ADC DUAL SMD SOIC28 112 |

| DDC112UK/1K | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Dual Current Input 20-Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。