- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295495 > DDC112U/1K (TEXAS INSTRUMENTS INC) 2-CH 20-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | DDC112U/1K |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 2-CH 20-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO28 |

| 封裝: | GREEN, PLASTIC, SOIC-28 |

| 文件頁數(shù): | 15/34頁 |

| 文件大小: | 776K |

| 代理商: | DDC112U/1K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

DDC112

22

SBAS085B

www.ti.com

RETRIEVAL

BEFORE CONV TOGGLES

(CONTINUOUS MODE)

This is the most straightforward method. Data retrieval be-

gins soon after DVALID goes LOW and finishes before

CONV toggles, see Figure 24. For best performance, data

retrieval must stop t28 before CONV toggles. This method is

the most appropriate for longer integration times. The maxi-

mum time available for readback is TINT – t27 – t28.

For DCLK and CLK = 10MHz, the maximum number of

DDC112s that can be daisy-chained together is:

Ts

INT

DCLK

–

.

431 2

40

τ

Where

τ

DCLK is the period of the data clock. For example, if

TINT = 1000s and DCLK = 10MHz, the maximum number of

DDC112s is:

1000

431 2

40 100

142 2

142

112

=→

ss

ns

DDC

s

–

.

()(

)

.

RETRIEVAL

AFTER CONV TOGGLES

(CONTINUOUS MODE)

For shorter integration times, more time is available if data

retrieval begins after CONV toggles and ends before the new

data is ready. Data retrieval must wait t29 after CONV toggles

before beginning. Figure 25 shows an example of this. The

maximum time available for retrieval is t27 – t29 – t26

(421.2

s – 10s – 2s for CLK = 10MHz), regardless of T

INT.

The maximum number of DDC112s that can be daisy-

chained together is:

409 2

40

.

s

DCLK

τ

For DCLK = 10MHz, the maximum number of DDC112s is

102.

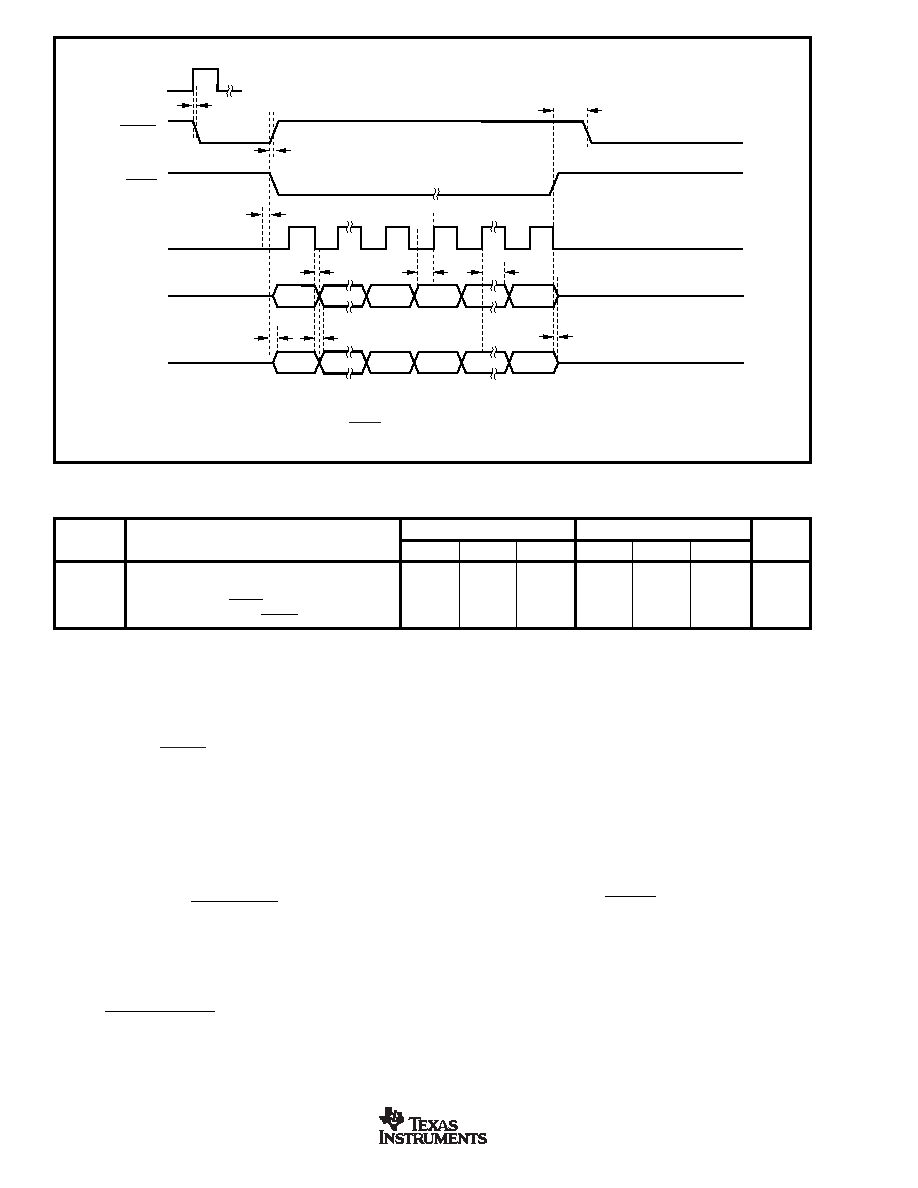

FIGURE 23. Timing Diagram When Using the DIN Function of the DDC112.

t

18

t

14

t

20

t

21

t

22

t

23

t

24

t

25

Output Disabled

Output Enabled

Output Disabled

CLK

DVALID

DXMIT

DCLK(1)

DIN

Input A

Bit 1

Input E

Bit 20

Input F

Bit 1

Input F

Bit 20

MSB

Output Disabled

Output Enabled

LSB

Output Disabled

MSB

DOUT

NOTE: (1) Disable DCLK (preferably LOW) when DXMIT is HIGH.

t

26

t

22A, t22B

TABLE X. Timing for the DDC112 Data Retrieval Using DIN.

CLK = 10MHz

CLK = 15MHz

SYMBOL

DESCRIPTION

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

t24

Set-Up Time From DIN to Rising Edge of DCLK

10

5

ns

t25

Hold Time For DIN After Rising Edge of DCLK

10

ns

t26

Hold Time for DXMIT HIGH Before Falling

2

1.33

s

Edge of DVALID

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DDC123JK-7-F | 100 mA, 50 V, 2 CHANNEL, NPN, Si, SMALL SIGNAL TRANSISTOR |

| DDL24W700G30LF | 24 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, SOLDER, SOCKET |

| DDV36W443G40LF | 36 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, SOLDER, SOCKET |

| DDV47W143G30LF | 47 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, SOLDER, SOCKET |

| DDV47W143H40LF | 47 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, SOLDER, SOCKET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DDC112UG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Dual Current Input 20-Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| DDC112UK | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Dual Current Input 20-Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| DDC112UK | 制造商:Texas Instruments 功能描述:DUAL CURRENT INPUT 20 BIT ANALOG/DIGITAL |

| DDC112UK | 制造商:Texas Instruments 功能描述:20BIT ADC DUAL SMD SOIC28 112 |

| DDC112UK/1K | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Dual Current Input 20-Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。