- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369673 > CT1820 (Aeroflex Inc.) CT1820 Data Terminal Bit Processor for MIL-STD-1553 A & B PDF資料下載

參數(shù)資料

| 型號(hào): | CT1820 |

| 廠商: | Aeroflex Inc. |

| 英文描述: | CT1820 Data Terminal Bit Processor for MIL-STD-1553 A & B |

| 中文描述: | CT1820數(shù)據(jù)終端位處理器的MIL - STD - 1553的阿 |

| 文件頁數(shù): | 1/10頁 |

| 文件大小: | 144K |

| 代理商: | CT1820 |

eroflex Circuit T

echnology

– Data Bus Modules For The Future SCDCT1820 REV D 6/25/99

Features

Performs Encoder, Decoder, Logic and Control functions of a Data Bus Terminal to

MIL-STD-1553 specifications, including Address, Mode Code and Broadcast Decoding and

Terminal Fail Safe

Flexibility - all control lines accessible

Parallel tri-state subsystem l/O bus compatible with both 16 bit and 8 bit systems

Dual rank l/O registers for versatile subsystem tlmlng

Operates from +5VDC @ 40mA typical (25mA CT1820)

Self-contained oscillator and clock driver

Look-ahead serial receive data output

Self-test, on-line wraparound, plus off-line capability

1

General Description

The CT1555-3/CT1820 Bit Processor Unit (BPU) is an advanced Hybrid Microcircuit that provides the interface between a

MIL-STD-1553 Transceiver such as CT3231M or CT3232M, and the subsystem internal parallel data bus. The unit can be

employed as the mux bus interface for Remote Subsystems or Master Terminal Bus Controllers, thus providing a common

interface for all systems communicating over the bus.

The unit places no restrictions on Command, Response or polling operations as it transfers all Command, Status and Data

words from the bus to parallel output lines, together with error information, bus status and handshaking signals. It also

contains 5 Bit Address Recognition, Broadcast and Mode Code Decode, Terminal Fail Safe Signal and Self Test.

In the transmit mode, it accepts parallel data from the user and transmits Command, Status and Data words, under

subsystem control, to the data bus. Positive handshaking signals provide logic control synchronisation between the unit

and the subsystem for direct data flow.

The hybrid is completely compatible with all the electrical and functional spec requirements of MIL-STD-1553 A & B.

Data Terminal Bit Processor

for MIL-STD-1553 A & B

CT1820

F

I

E

I

D

C

E

R

T

A

O

F

L

E

X

L

A

B

S

N

C

ISO

9001

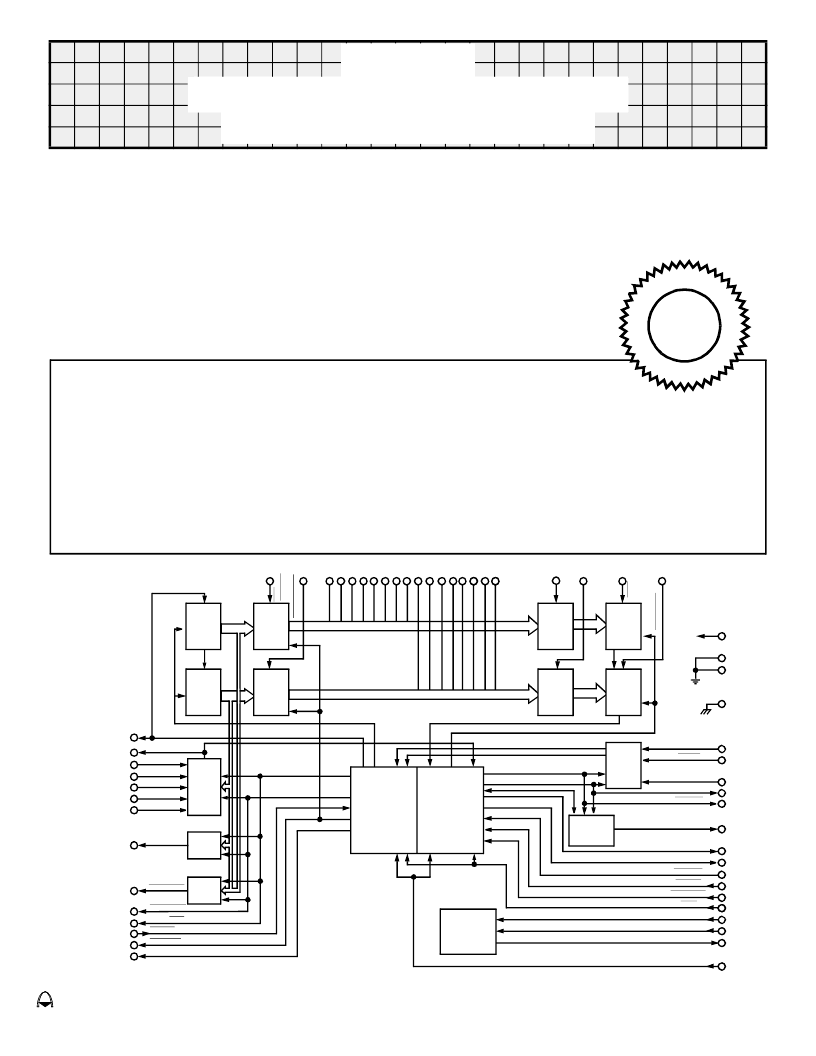

Figure 1 – Functional Diagram

4

36

12

SERIAL DATA OUT

32

8

9

10

13

14

16

33

31

37

7

4

4

4

4

5

4

4

4

2

3

4

5

6

5

5

5

4

4

4

5

11

34

20

21

22

19

25

26

15

27

28

24

23

38

35

30

29

18

17

1

FIRST

RANK

REC’V

REG

DO - D7

SECOND

RANK

REC’V

REG

DO - D7

FIRST

RANK

REC’V

REG

D8 - D15

SECOND

RANK

REC’V

REG

D8 - D15

FIRST

RANK

XMT

REG

DO - D7

SECOND

RANK

XMT

REG

DO - D7

FIRST

RANK

XMT

REG

D8 - D15

SECOND

RANK

XMT

REG

D8 - D15

MANCHESTER

DECODER

&

CONTROL LOGIC

MANCHESTER

ENCODER

&

CONTROL LOGIC

OSC

&

CLOCK

DRIVER

39

40

BROAD-

CAST

DECODE

RT ENABLE

(MSB) A4

A3

A2

A1

(LSB) A0

5 BIT

ADDRESS

{

BROADCAST

MODE CODE

VALID WORD

COMM/DATA SYNC

MODE

CODE

DECODE

DEC RST

TAKE DATA

DSC OUT

D

(

D

D

D

D

D

D

D

D

D

D

D

D

D

(

(

S

I

L

D

2

L

L

D

L

GND

GND

Vcc

+5V

CASE

DATA IN

DATA IN

BIT SELECT

DATA OUT

DATA OUT

FAIL SAFE

SEND DATA

ESCOUT

SYNC SEL

ENC ENA

OUTPUT INH

MRST

+5V OSC / CLOCK POWER

XTAL

CLOCK OUT

CLOCK IN

D

D

S

BUILT IN

TEST

SELECT

ADDRESS

DECODE

FAIL SAFE

TIMER

&

CONTROL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CT1991-1-20 | MIL-STD-1553B Remote Terminal, Bus Controller, or Passive Monitor Hybrid with Status Word Control |

| CT1990-1-20 | MIL-STD-1553B Remote Terminal, Bus Controller, or Passive Monitor Hybrid with Status Word Control |

| CT19901 | MIL-STD-1553B Remote Terminal, Bus Controller, or Passive Monitor Hybrid with Status Word Control |

| CT1995 | MIL-STD-1553B Remote Terminal, Bus Controller, or Passive Monitor Hybrid with Status Word Control |

| CT1995-20 | MIL-STD-1553B Remote Terminal, Bus Controller, or Passive Monitor Hybrid with Status Word Control |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CT1839 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Output Stage |

| CT1842 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Output Stage |

| CT18-4BLK-C | 制造商:GC Electronics 功能描述: |

| CT18-4BLK-M | 制造商:GC Electronics 功能描述: |

| CT18-4NAT-C | 制造商:GC Electronics 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。