- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1905 > ATF1508RE-7AU100 (Atmel)IC CPLD EE 128MC 5NS 100-TQFP PDF資料下載

參數(shù)資料

| 型號: | ATF1508RE-7AU100 |

| 廠商: | Atmel |

| 文件頁數(shù): | 52/54頁 |

| 文件大小: | 0K |

| 描述: | IC CPLD EE 128MC 5NS 100-TQFP |

| 標準包裝: | 90 |

| 系列: | ATF15xx |

| 可編程類型: | 系統(tǒng)內(nèi)可編程(最少 10,000 次編程/擦除循環(huán)) |

| 最大延遲時間 tpd(1): | 7.5ns |

| 電壓電源 - 內(nèi)部: | 3 V ~ 3.6 V |

| 宏單元數(shù): | 128 |

| 輸入/輸出數(shù): | 80 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP(14x14) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 608 (CN2011-ZH PDF) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當前第52頁第53頁第54頁

Introduction

1-4

Atmel ATF15xx Family: ISP Devices User Guide

A device residing in any location in the JTAG chain can be programmed exclusive of all

others. You can use the Atmel-ISP software to place all other devices except the one to

be programmed in the JTAG Bypass mode. When the other devices are placed in this

mode, a 1-bit flow-through register appears between the TDI and TDO pins for these

devices. During a programming operation, JTAG programming data passes through

devices in the JTAG Bypass mode but is loaded into the device that is to be pro-

grammed. This allows only the device you want to program to be loaded with JEDEC

fuse data.

1.3

Design

Considerations

Performing ISP on Atmel ISP devices requires that you reserve design resources for the

JTAG interface. You will need to reserve four I/O pins for the TMS, TDI, TDO and TCK

pins. The pin numbers for these pins depend on which Atmel ISP device you are using

and its package type. Refer to Table 1-1 for pinout information. The JTAG standard also

requires that the TMS and TDI pins be pulled up for each device in the JTAG chain. The

Atmel ISP devices have an internal pull-up feature for these pins which, when enabled,

saves the need for external pull-up resistors. Once you have reserved logic resources

for the JTAG interface, you can program, verify and erase any Atmel ISP device using

the Atmel-ISP software.

Note:

Even though you must reserve certain I/O pins in your design for the JTAG

interface, you can still implement buried logic functions in the macrocells associ-

ated with these pins.

To use ISP to program Atmel devices, you must enable the JTAG interface. An optional

but recommended practice is to also enable the TMS and TDI internal pull-ups. Enabling

the JTAG interface requires choosing specific Atmel device types before compiling your

design. This procedure is outlined below for Atmel-Synario and Atmel-WinCUPL. If

you need to enable Atmel fitter properties for other software platforms, please contact

Atmel PLD Applications.

1.3.1

JTAG Interface with

Atmel-Synario

To enable the JTAG interface with Atmel-Synario and multi-vendor Synario, you’ll need

to select an Atmel ISP device type first. You can change fitter property settings to enable

the TDI and TMS internal pull-ups or the pin-keeper circuits.

Note:

If you use an Atmel ISP device type for a design that uses the JTAG interface

pins as logic I/O pins, Atmel-Synario will generate an error.

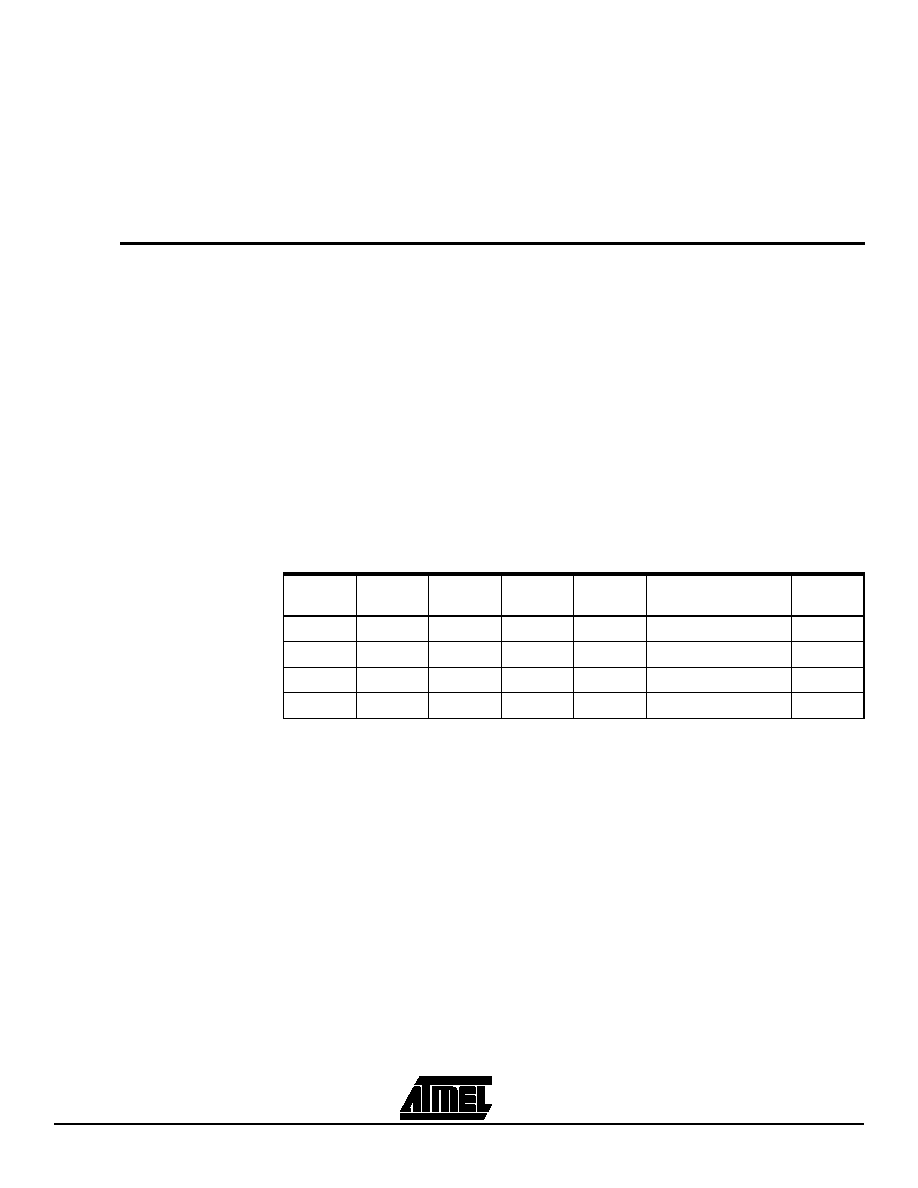

Table 1-1. Atmel ISP Device JTAG Pinout

JTAG

Pin

44-pin

TQFP

44-pin

PLCC

68-pin

PLCC

84-pin

PLCC

100-pin

PQFP

100-pin

TQFP

160-pin

PQFP

TDI

1

712

146

4

9

TDO

32385771

7573

112

TMS

7

13

19

23

17

15

22

TCK

26325062

6462

99

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ATF16LV8C-10SI | IC PLD EE 8CELL 3V LP 20-SOIC |

| ATF16V8BQL-15XC | IC PLD 15NS 20TSSOP |

| ATF16V8C-7XU | IC PLD 7NS 20TSSOP |

| ATF16V8CZ-15XC | IC PLD 15NS 20TSSOP |

| ATF20V8BQL-15PU | IC PLD 15NS 24DIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATF1508RE-7CU132 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Highperformance CPLD |

| ATF1508SE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Family Datasheet |

| ATF1508SE(L) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATF1502/04/08/16SE(L) Preliminary [Updated 9/02. 69 Pages] Second Generation Industry Compatible 5V Logic Doubling CPLDs 32-512 Macrocells. standard & low power w/ISP |

| ATF1508SL | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Family Datasheet |

| ATF1508Z | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:High Performance E2PLD |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。