- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373980 > ADE7758 (Analog Devices, Inc.) Poly Phase Multifunction Energy Metering IC with Per Phase Information PDF資料下載

參數(shù)資料

| 型號(hào): | ADE7758 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Poly Phase Multifunction Energy Metering IC with Per Phase Information |

| 中文描述: | 多相多功能電能計(jì)量IC每相位信息 |

| 文件頁(yè)數(shù): | 26/68頁(yè) |

| 文件大?。?/td> | 1584K |

| 代理商: | ADE7758 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

ADE7758

PERIOD MEASUREMENT

The ADE7758 provides the period or frequency measurement

of the line voltage. The period is measured on the phase

specified by Bit 0 to Bit 1 of the MMODE register. The period

register is an unsigned 12-bit FREQ register and is updated

every 4 periods of the selected phase.

Rev. A | Page 26 of 68

Bit 7 of the LCYCMODE selects whether the period register

displays the frequency or the period. Setting this bit to logic

high causes the register to display the period. The default

setting is logic low, which causes the register to display the

frequency.

When set to measure the period, the resolution of this register is

96/CLKIN per LSB (9.6 μs/LSB when CLKIN is 10 MHz),

which represents 0.06% when the line frequency is 60 Hz. At 60

Hz, the value of the period register is 1737d. At 50 Hz, the value

of the period register is 2084d. When set to measure frequency,

the value of the period register is approximately 960d at 60 Hz

and 800d at 50 Hz. This is equivalent to 0.0625 Hz/LSB.

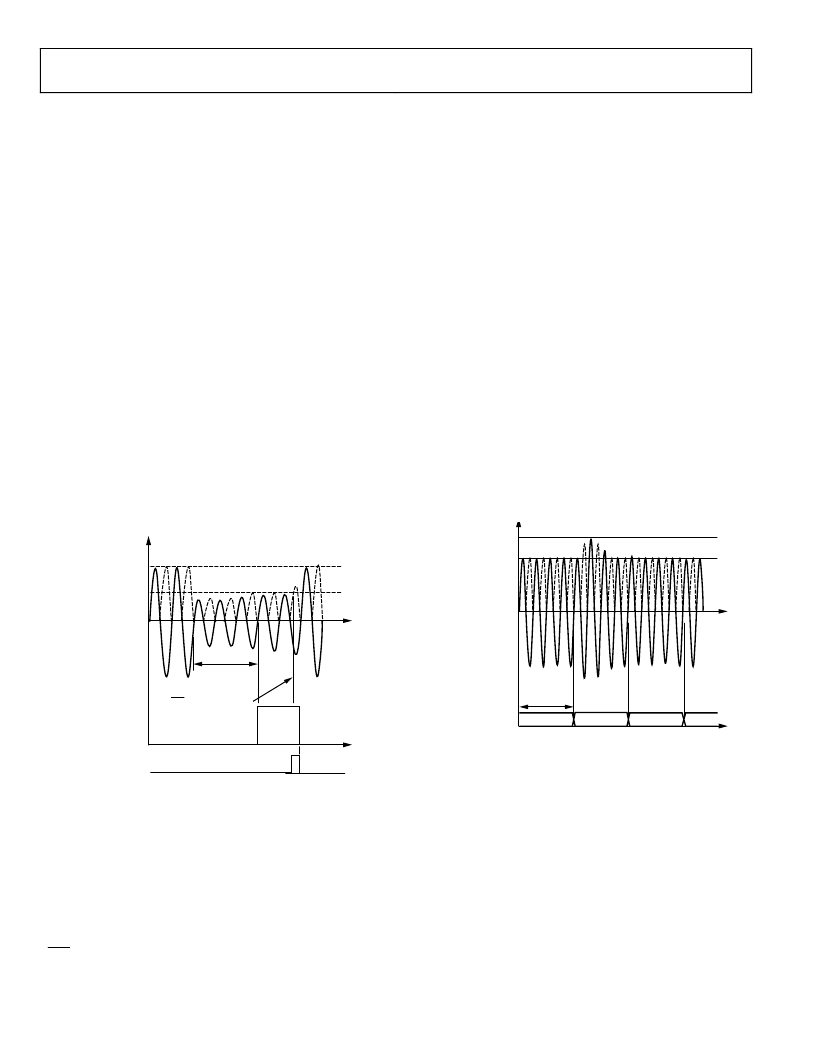

LINE VOLTAGE SAG DETECTION

The ADE7758 can be programmed to detect when the absolute

value of the line voltage of any phase drops below a certain peak

value, for a number of half cycles. Each phase of the voltage

channel is controlled simultaneously. This condition is

illustrated in Figure 57.

0

SAGLVL[7:0]

FULL-SCALE

READ RSTATUS

REGISTER

SAGCYC[7:0] = 0x06

6 HALF CYCLES

SAG INTERRUPT FLAG

(BIT 3 TO BIT 5 OF

STATUS REGISTER)

VAP, VBP, OR VCP

SAG EVENT RESET LOW

WHEN VOLTAGE CHANNEL

EXCEEDS SAGLVL[7:0]

Figure 57. ADE7758 SAG Detection

Figure 57 shows a line voltage fall below a threshold which is set

in the SAG level register (SAGLVL[7:0]) for nine half cycles.

Since the SAG cycle register indicates a six half-cycle threshold

(SAGCYC[7:0] = 0x06), the SAG event is recorded at the end of

the sixth half cycle by setting the SAG flag of the corresponding

phase in the interrupt status register (Bit 1 to Bit 3 in the

interrupt status register). If the SAG enable bit is set to Logic 1

for this phase (Bit 1 to Bit 3 in the interrupt mask register), the

IRQ logic output goes active low (see the ADE7758 Interrupts

section). The phases are compared to the same parameters

defined in the SAGLVL and SAGCYC registers.

SAG LEVEL SET

The contents of the single-byte SAG level register, SAGLVL[0:7],

are compared to the absolute value of Bit 6 to Bit 13 from the

voltage waveform samples. For example, the nominal maximum

code of the voltage channel waveform samples with a full-scale

signal input at 60 Hz is 0x249C (see the Voltage Channel

Sampling section). Bit 13 to Bit 6 are 0x92. Therefore, writing

0x92 to the SAG level register puts the SAG detection level at

full scale and sets the SAG detection to its most sensitive value.

The detection is made when the content of the SAGLVL[7:0]

register is greater than the incoming sample. Writing 0x00 puts

the SAG detection level at 0. The detection of a decrease of an

input voltage is in this case disabled.

PEAK VOLTAGE DETECTION

The ADE7758 can record the peak of the voltage waveform and

produce an interrupt if the current exceeds a preset limit.

Peak Voltage Detection Using the VPEAK Register

The peak absolute value of the voltage waveform within a fixed

number of half-line cycles is stored in the VPEAK register.

Figure 58 illustrates the timing behavior of the peak voltage

detection.

0

L2

L1

CONTENT OF

VPEAK[7:0]

00

L1

L2

L1

NREGISTER

VOLTAGE WAVEFORM

(PHASE SELECTED BY

PEAKSEL[2:4]

IN MMODE REGISTER)

Figure 58. Peak Voltage Detection Using the VPEAK Register

Note that the content of the VPEAK register is equivalent to Bit 6

to Bit 13 of the 16-bit voltage waveform sample. At full-scale

analog input, the voltage waveform sample at 60 Hz is 0x249C.

The VPEAK at full-scale input is, therefore, expected to be 0x92.

In addition, multiple phases can be activated for the peak

detection simultaneously by setting multiple bits to logic high

among the PEAKSEL[2:4] bits in the MMODE register. These

bits select the phase for both voltage and current peak measure-

ments. Note that if more than one bit is set, the VPEAK and

IPEAK registers can hold values from two different phases, i.e.,

the voltage and current peak are independently processed (see

the Peak Current Detection section).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADE7758ARW | Poly Phase Multifunction Energy Metering IC with Per Phase Information |

| ADE7758ARWRL | Poly Phase Multifunction Energy Metering IC with Per Phase Information |

| ADE7758ARWZ | Poly Phase Multifunction Energy Metering IC with Per Phase Information |

| ADE7758ARWZRL | Poly Phase Multifunction Energy Metering IC with Per Phase Information |

| ADE7759ARSRL | Active Energy Metering IC with di/dt Sensor Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADE7758ARW | 制造商:Analog Devices 功能描述:Energy Measurement 24-Pin SOIC W 制造商:Analog Devices 功能描述:IC ENERGY METER |

| ADE7758ARWRL | 制造商:Analog Devices 功能描述:Energy Measurement 24-Pin SOIC W T/R 制造商:Analog Devices 功能描述:IC ENERGY METER |

| ADE7758ARWZ | 功能描述:IC ENERGY METERING 3PHASE 24SOIC RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測(cè)量 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:* |

| ADE7758ARWZ | 制造商:Analog Devices 功能描述:ENERGY METERING IC 制造商:Analog Devices 功能描述:IC, POLY-PHASE ENERGY METERING, SOIC-24 |

| ADE7758ARWZ | 制造商:Analog Devices 功能描述:IC ENERGY METER 3 PHASE SOIC-24 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。