- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373980 > ADE7169ASTF16 (ANALOG DEVICES INC) Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver PDF資料下載

參數(shù)資料

| 型號(hào): | ADE7169ASTF16 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 模擬信號(hào)調(diào)理 |

| 英文描述: | Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver |

| 中文描述: | ANALOG CIRCUIT, PQFP64 |

| 封裝: | MS-026BCD, LQFP-64 |

| 文件頁(yè)數(shù): | 104/140頁(yè) |

| 文件大小: | 1359K |

| 代理商: | ADE7169ASTF16 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)當(dāng)前第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)

ADE7169F16

Preliminary Technical Data

Rev. PrD | Page 104 of 140

1

0

8-Bit Autoreload Timer/Counter. TH1 holds a value that is to be reloaded into

TL1 each time it overflows.

Timer/Counter 1 Stopped.

Timer 0 Gating Control.

Set by software to enable Timer/Counter 0 only while the INT0 pin is high and the TR0 control bit

is set.

Cleared by software to enable Timer 0 whenever the TR0 control bit is set.

Timer 0 Timer or Counter Select Bit.

Set by software to the select counter operation (input from T0 pin).

Cleared by software to the select timer operation (input from internal system clock).

Timer 0 Mode Select Bits

M1

M0

Description

0

0

TH0 operates as an 8-bit timer/counter. TL0 serves as a 5-bit prescaler.

0

1

16-Bit Timer/Counter. TH0 and TL0 are cascaded; there is no prescaler.

1

0

8-Bit Autoreload Timer/Counter. TH0 holds a value that is to be reloaded into

TL0 each time it overflows.

1

1

TL0 is an 8-bit timer/counter controlled by the standard Timer 0 control bits.

TH0 is an 8-bit timer only, controlled by Timer 1 control bits.

1

1

3

Gate0

0

2

C_T0

0

1-0

T0_M1,

T0_M0

00

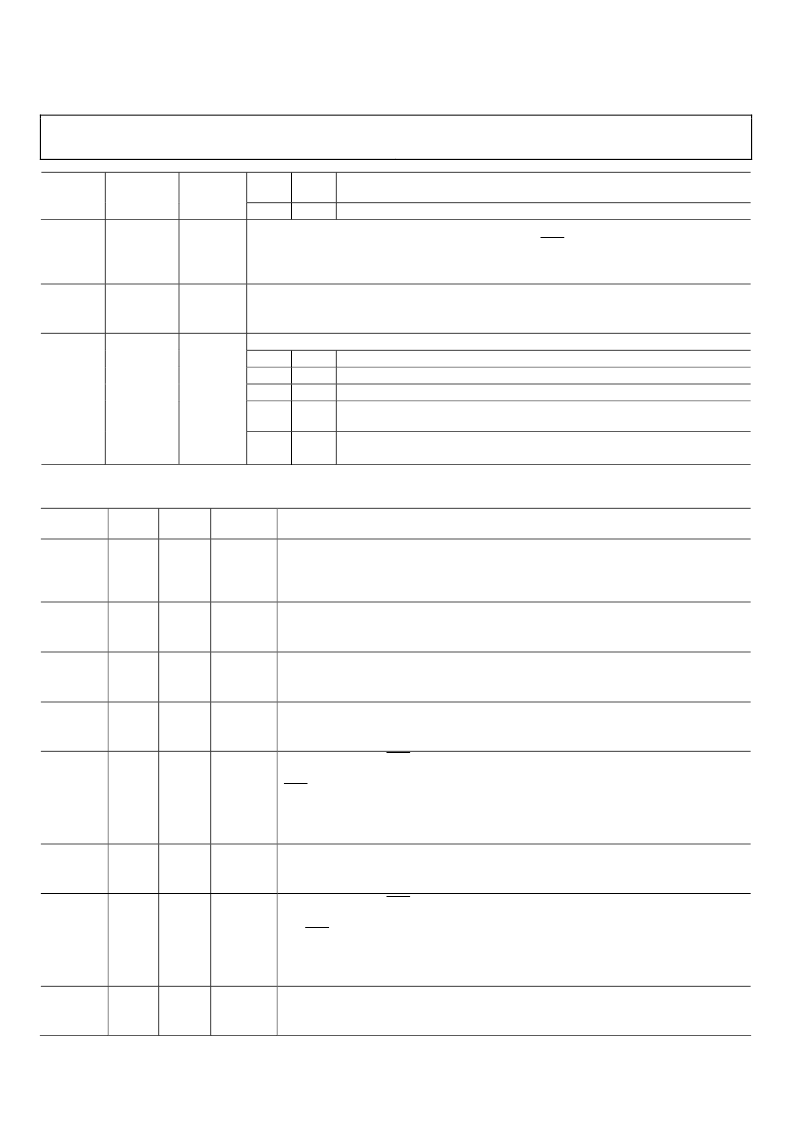

Table 95. Timer/Counter 0 and 1 Control SFR (TCON, 0x88)

Bit

Location

Addr.

Name

7

0x8F

TF1

Bit

Bit

Default

Value

0

Description

Timer 1 Overflow Flag.

Set by hardware on a Timer/Counter 1 overflow.

Cleared by hardware when the program counter (PC) vectors to the interrupt service

routine.

Timer 1 Run Control Bit.

Set by the user to turn on Timer/Counter 1.

Cleared by the user to turn off Timer/Counter 1.

Timer 0 Overflow Flag.

Set by hardware on a Timer/Counter 0 overflow.

Cleared by hardware when the PC vectors to the interrupt service routine.

Timer 0 Run Control Bit.

Set by the user to turn on Timer/Counter 0.

Cleared by the user to turn off Timer/Counter 0.

External Interrupt 1 (INT1) Flag.

Set by hardware by a falling edge or by a zero level applied to the external interrupt pin,

INT1, depending on the state of Bit IT1.

Cleared by hardware when the PC vectors to the interrupt service routine only if the

interrupt was transition-activated. If level-activated, the external requesting source controls

the request flag rather than the on-chip hardware.

External Interrupt 1 (IE1) Trigger Type.

Set by software to specify edge-sensitive detection, that is, 1-to-0 transition.

Cleared by software to specify level-sensitive detection, that is, zero level.

External Interrupt 0 (INT0) Flag.

Set by hardware by a falling edge or by a zero level being applied to the external interrupt

pin, INT0, depending on the statue of Bit IT0.

Cleared by hardware when the PC vectors to the interrupt service routine only if the

interrupt was transition-activated. If level-activated, the external requesting source controls

the request flag rather than the on-chip hardware.

External Interrupt 0 (IE0) Trigger Type.

Set by software to specify edge-sensitive detection, that is, 1-to-0 transition.

Cleared by software to specify level-sensitive detection, that is, zero level.

6

0x8E

TR1

0

5

0x8D

TF0

0

4

0x8C

TR0

0

3

0x8B

IE1

1

0

2

0x8A

IT1

1

0

1

0x89

IE0

1

0

0

0x88

IT0

1

0

__________________________________________

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADE7169ASTF16-RL | Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver |

| ADE7169ASTZF16 | Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver |

| ADE7169ASTZF16-RL | Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver |

| ADE7169F16 | Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver |

| ADE7751 | Energy Metering IC with On-Chip Fault Detection |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADE7169ASTF16-RL | 制造商:AD 制造商全稱:Analog Devices 功能描述:Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver |

| ADE7169ASTZF16 | 功能描述:IC ENERGY METER 1PHASE 64LQFP RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測(cè)量 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:* |

| ADE7169ASTZF16-RL | 功能描述:IC ENERGY METER 1PHASE 64LQFP RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測(cè)量 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:* |

| ADE7169F16 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver |

| ADE75 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Single-Phase Energy Measurement IC with 8052 MCU, RTC and LCD driver |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。