- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375249 > AD9854ASQ (ANALOG DEVICES INC) CMOS 300 MHz Quadrature Complete-DDS PDF資料下載

參數(shù)資料

| 型號: | AD9854ASQ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | XO, clock |

| 英文描述: | CMOS 300 MHz Quadrature Complete-DDS |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 30 MHz, PQFP80 |

| 封裝: | MS-026-BEC, LQFP-80 |

| 文件頁數(shù): | 24/44頁 |

| 文件大小: | 433K |

| 代理商: | AD9854ASQ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

AD9854

–24–

REV. 0

2. Stop using the hold pin function, then ramp-down the output

amplitude using the digital multiplier stages and the Shaped

Keying pin, Pin 30, or via program register control (addresses

21–24 hex).

3. Stop and abruptly terminate the transmission using the CLR

ACC2 bit.

4. Continue chirp by reversing direction and returning to the

previous, or another, destination frequency in a linear or user-

directed manner. If this involves going down in frequency, a

negative 48-bit Delta Frequency Word (the MSB is set to

“1”) must be loaded into registers 10–15 hex. Any decreasing

frequency step of the Delta Frequency Word requires the MSB

to be set to logic high.

5. Continue chirp by immediately returning to the F1 beginning

frequency in a sawtooth fashion and repeat the previous chirp

process again. This is where CLR ACC1 control bit is used.

An automatic, repeating chirp can be setup using the 32-bit

Update Clock to issue CLR ACC1 commands at precise time

intervals. Adjusting the timing intervals or changing the Delta

Frequency Word will change the chirp range. It is incumbent

upon the user to balance the chirp duration and frequency

resolution to achieve the proper frequency range.

BPSK (Mode 100)

Binary, biphase or bipolar phase shift keying is a means to rapidly

select between two preprogramming 14-bit output phase offsets

that will identically affect both the I and Q outputs of the AD9854.

The logic-state of Pin 29, BPSK pin, controls the selection of

Phase Adjust register number 1 or 2. When low, Pin 29 selects

Phase Adjust register 1; when high, Phase Adjust register 2 is

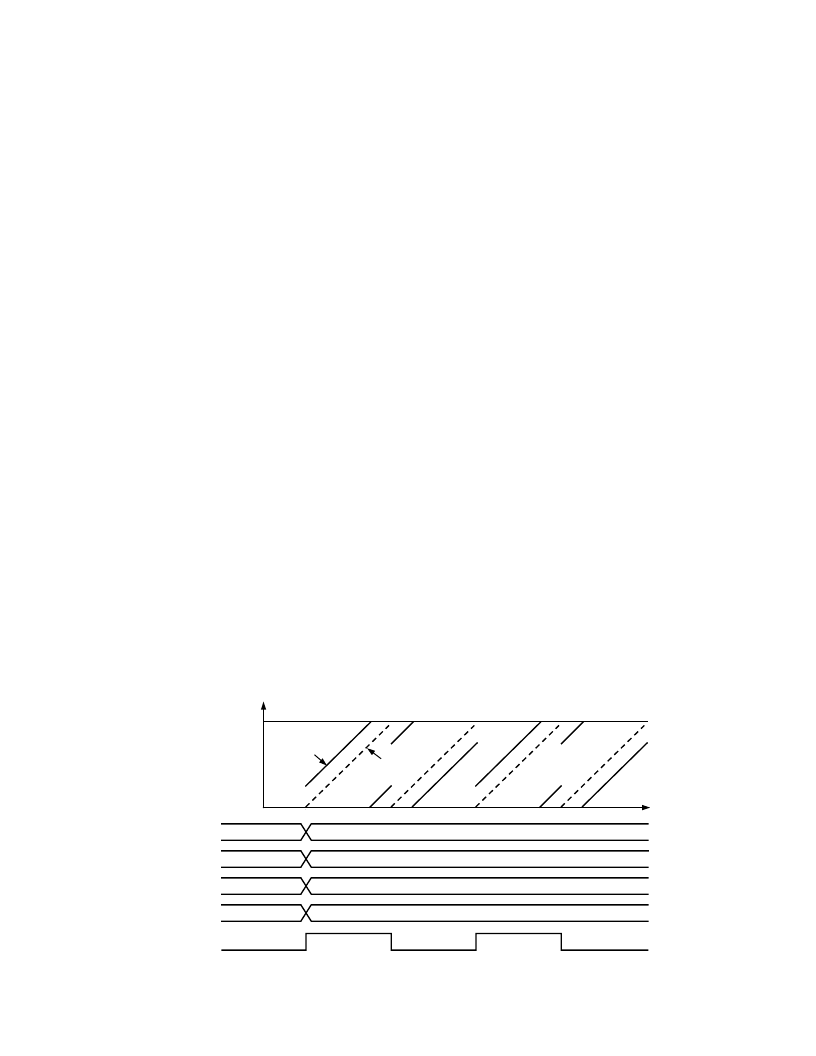

selected. Figure 48 illustrates phase changes made to four cycles

of an output carrier.

Basic BPSK programming steps:

1. Program a carrier frequency into Frequency Tuning Word 1.

2. Program appropriate 14-bit phase words in Phase Adjust

registers 1 and 2.

3. Attach BPSK data source to Pin 29.

4. Activate I/O Update pulse when ready.

If phase shift keying is not the objective, but rather a broader

range of phase offsets is needed, the user should select the Single

Tone mode and program Phase Adjust register 1 using the serial or

high-speed parallel programming bus.

I/O Port Buffers

—100 MHz, 8-bit parallel or 10 MHz serial

loading, SPI-compatible. The programming mode is selected

externally via the serial/parallel (S/P Select) pin. I/O Buffers can

be written to, or read from, according to the signals supplied to

the Read (RDB) and Write pins (WRB) and the 6-bit address

(A0–A5) in the parallel mode or to CSB, SCLK and SDIO pins

in the Serial mode.

Data in the I/O Port Buffers is stored until overwritten by changes

in program instructions supplied by the user or until power is

removed. An I/O Update clocks-in the data from the I/O Buffers

to the DDS Programming Registers where it is executed.

AM

—amplitude modulation of the I and Q DACs is possible

using the I/O port to control 12-bit digital multiplier stages that

precede the DACs. The multipliers can also be used to set the

DAC outputs between zero- and full-scale for static amplitude

adjustment. Both I and Q DAC amplitudes are individually

programmable. See the “Shaped On/Off Keying” description

for more information. Shaped keying function does not apply to

the Q DAC when configured as a Control DAC. In this instance,

the user is in control of the Control DAC output level via the

12-bit QDAC register at address 26 and 27 hex of the pro-

gramming registers

High-Speed Comparator

—optimized for high speed, >300 MHz

toggle rate, low jitter, sensitive input, built-in hysteresis and

an output level of 1 V p-p minimum into 50

or CMOS logic

levels into high impedance loads. The comparator can be sepa-

rately powered down to conserve power. This comparator is used

in “clock generator” applications to square up a bandpass or

low-pass filtered sine wave.

Eight-Bit Ramp Rate Clock

—when Shaped On/Off Keying is

engaged, this down-counter takes the system clock (300 MHz

maximum), and divides it by an 8-bit binary value (programmed

by the user) to produce a user-defined clock. The clock outputs

one pulse every time the counter counts down to zero. This clock is

BPSK DATA

360

0

P

MODE

FTW1

PHASE ADJUST 1

000 (DEFAULT)

0

PHASE ADJUST 2

100 (BPSK)

F1

270 DEGREES

90 DEGREES

PHASE AFTER

ONSET

PHASE BEFORE

ONSET

Figure 48. BPSK Mode

相關PDF資料 |

PDF描述 |

|---|---|

| AD9854AST | CMOS 300 MHz Quadrature Complete-DDS |

| AD9856AST | CMOS 200 MHz Quadrature Digital Upconverter |

| AD9856 | CMOS 180 MHz Quadrature Digital Upconverter(時鐘頻率為180MHz,CMOS的積分上變頻器) |

| AD9857 | CMOS 200 MSPS 14-Bit Quadrature Digital Upconverter |

| AD9857AST | CMOS 200 MSPS 14-Bit Quadrature Digital Upconverter |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD9854ASQZ | 制造商:Analog Devices 功能描述:Direct Digital Synthesizer 300MHz 2-DAC 12-Bit Parallel/Serial 80-Pin LQFP 制造商:Analog Devices 功能描述:Communication IC |

| AD9854AST | 制造商:Analog Devices 功能描述:Direct Digital Synthesizer 300MHz 2-DAC 12-Bit Parallel/Serial 80-Pin LQFP Tray 制造商:Rochester Electronics LLC 功能描述:200 MHZ QUADRATURE DDS SYNTHESIZER - Tape and Reel 制造商:Analog Devices 功能描述:IC SEMICONDUCTOR ((NS)) |

| AD9854ASTZ | 功能描述:IC DDS QUADRATURE CMOS 80-LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數(shù)字合成 (DDS) 系列:- 產(chǎn)品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調(diào)節(jié)字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9854ASVZ | 制造商:Analog Devices 功能描述:CMOS 300 MSPS QUADRATURE COMPLETE DDS 制造商:Analog Devices 功能描述:CMOS 300 MSPS QUADRATURE COMPLETE DDS - Trays 制造商:Analog Devices 功能描述:SYNTHESIZER 制造商:Analog Devices 功能描述:Complete DDS Quadrature 300MSPS TQFP80 |

| AD9854PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:CMOS 300 MSPS Quadrature Complete DDS |

發(fā)布緊急采購,3分鐘左右您將得到回復。