- 您現在的位置:買賣IC網 > PDF目錄375238 > AD7750AN (ANALOG DEVICES INC) Product-to-Frequency Converter PDF資料下載

參數資料

| 型號: | AD7750AN |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 模擬信號調理 |

| 英文描述: | Product-to-Frequency Converter |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, PDIP20 |

| 封裝: | PLASTIC, DIP-20 |

| 文件頁數: | 2/16頁 |

| 文件大小: | 195K |

| 代理商: | AD7750AN |

–2–

REV. 0

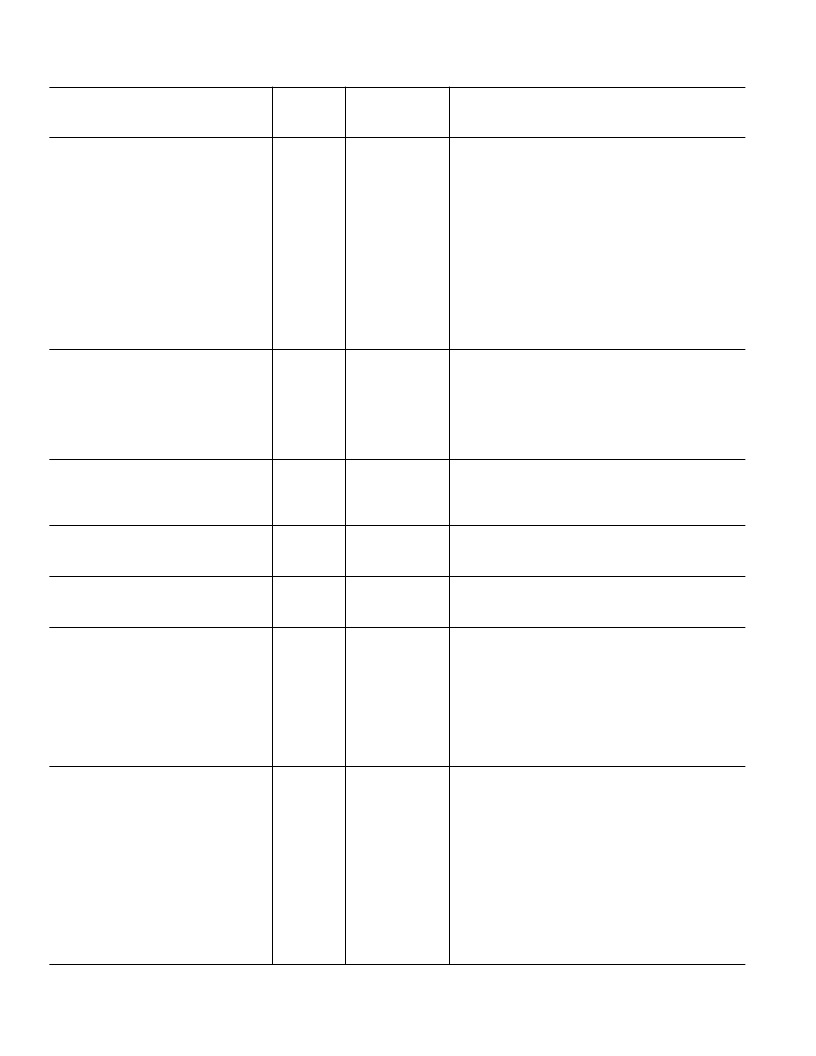

AD7750–SPECIFICATIONS

(V

DD

= 5 V

6

5%, AGND = 0V, DGND = 0 V, REFIN= +2.5V, CLKIN= 3.58 MHz

T

MN

to T

MAX

= –40

8

C to +85

8

C, ACDC = Logic Hgh)

A Version

–40

8

C to

+85

8

C

Parameter

Units

T est Conditions/Comments

ACCURACY

Measurement Error

1

Gain = 1

Channel 2 with Full-Scale Signal

Measured Over a Dynamic Range on Channel 1 of 500:1

Measured Over a Dynamic Range on Channel 1 of 1000:1

Measured Over a Dynamic Range on Channel 1 of 500:1

Measured Over a Dynamic Range on Channel 1 of 1000:1

CLK IN = 3.58 MHz, Line Frequency = 50 Hz

HPF Filter On, ACDC = 1

HPF Filter On, ACDC = 1

HPF Filter On, ACDC = 1, Mode 3, Channel 1 = 0 V

Channel 2 = 500 mV rms at 50 Hz

HPF Filter On, ACDC = 1, Mode 3, Channel 1 = 0 V

Channel 2 = 500 mV rms, Power Supply Ripple

250 mV at 50 Hz. See Figures 1 and 3.

0.2

0.3

0.2

0.4

% Reading max

% Reading max

% Reading max

% Reading max

Gain = 16

Phase Error Between Channels

Phase Lead 40

°

(PF = +0.8)

Phase Lag 60

°

(PF = –0.5)

Feedthrough Between Channels

Output Frequency Variation (F

OUT

)

Power Supply Rejection

Output Frequency Variation (F

OUT

)

±

0.2

±

0.2

Degrees (

°

) max

Degrees (

°

) max

0.0005

% Full-Scale max

0.03

% Full-Scale max

ANALOG INPUT S

Maximum Signal Levels

Input Impedance (DC)

Bandwidth

Offset Error

Gain Error

Gain Error Match

±

1

400

3.5

±

10

±

4

±

0.3

V max

k

min

kHz typ

mV typ

% Full-Scale typ

% Full-Scale typ

On Any Input, V

1+

, V

1–

, V

2+

and V

2–

. See Analog Inputs.

CLK IN = 3.58 MHz

CLK IN = 3.58 MHz, CLK IN/1024

REFERENCE INPUT

REF

IN

Input Voltage Range

2.7

2.3

50

V max

V min

k

min

2.5 V + 8%

2.5 V – 8%

Input Impedance

ON-CHIP REFERENCE

Reference Error

T emperature Coefficient

Nominal 2.5 V

±

200

55

mV max

ppm/

°

C typ

CLK IN

Input Clock Frequency

4.5

2

MHz max

MHz min

LOGIC INPUT S

FS, S1, S2, ACDC and G1

Input High Voltage, V

INH

Input Low Voltage, V

INL

Input Current, I

IN

Input Capacitance, C

IN

CLK IN

Input High Voltage, V

INH

Input Low Voltage, V

INL

2.4

0.8

±

10

10

V min

V max

μ

A max

pF max

V

DD

= 5 V

±

5%

V

DD

= 5 V

±

5%

T ypically 10 nA, V

IN

= 0 V to V

DD

4

0.4

V min

V max

LOGIC OUT PUT S

2

F1 and F2

Output High Voltage, V

OH

I

SOURCE

= 8 mA

V

DD

= 5 V

I

SINK

= 8 mA

V

DD

= 5 V

4.3

V min

Output Low Voltage, V

OL

0.5

V max

F

OUT

and REVP

Output High Voltage, V

OH

I

SOURCE

= 1 mA

V

DD

= 5 V

±

5%

I

SINK

= 200

μ

A

V

DD

= 5 V

±

5%

4

V min

Output Low Voltage, V

OL

0.4

±

10

15

V max

μ

A max

pF max

High Impedance Leakage Current

High Impedance Capacitance

相關PDF資料 |

PDF描述 |

|---|---|

| AD7750AR | Product-to-Frequency Converter |

| AD7751(中文) | Energy Metering IC with On-Chip Fault Detection(高精度容錯電子能量測量芯片) |

| AD7751 | Energy Metering IC with On-Chip Fault Detection(高精度容錯電子能量測量芯片) |

| AD7755(中文) | Energy Metering IC with Pulse Output(帶脈沖輸出的高精度電子能量測量芯片) |

| AD7755 | Energy Metering IC with Pulse Output(帶脈沖輸出的高精度電子能量測量芯片) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7750AN | 制造商:Analog Devices 功能描述:SEMICONDUCTOR ((NW)) |

| AD7750AR | 制造商:Rochester Electronics LLC 功能描述:PRODUCT TO FREQUENCY CONVERTER I.C. - Bulk |

| AD7750AR-REEL | 制造商:Analog Devices 功能描述: |

| AD7751 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Energy Metering IC With On-Chip Fault Detection |

| AD7751AAN | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述:PRODUCT TO FREQUENCY CONV - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。