- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄2018 > XRD98L62ACV-F (Exar Corporation)IC CCD DIGITIZER 12BIT 48TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XRD98L62ACV-F |

| 廠(chǎng)商: | Exar Corporation |

| 文件頁(yè)數(shù): | 4/37頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC CCD DIGITIZER 12BIT 48TQFP |

| 標(biāo)準(zhǔn)包裝: | 250 |

| 位數(shù): | 12 |

| 通道數(shù): | 1 |

| 電壓 - 電源,模擬: | 2.7 V ~ 3.6 V |

| 電壓 - 電源,數(shù)字: | 2.7 V ~ 3.6 V |

| 封裝/外殼: | 48-TQFP |

| 供應(yīng)商設(shè)備封裝: | 48-TQFP(7x7) |

| 包裝: | 托盤(pán) |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

XRD98L62

12

Rev. P2.00

Preliminary

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

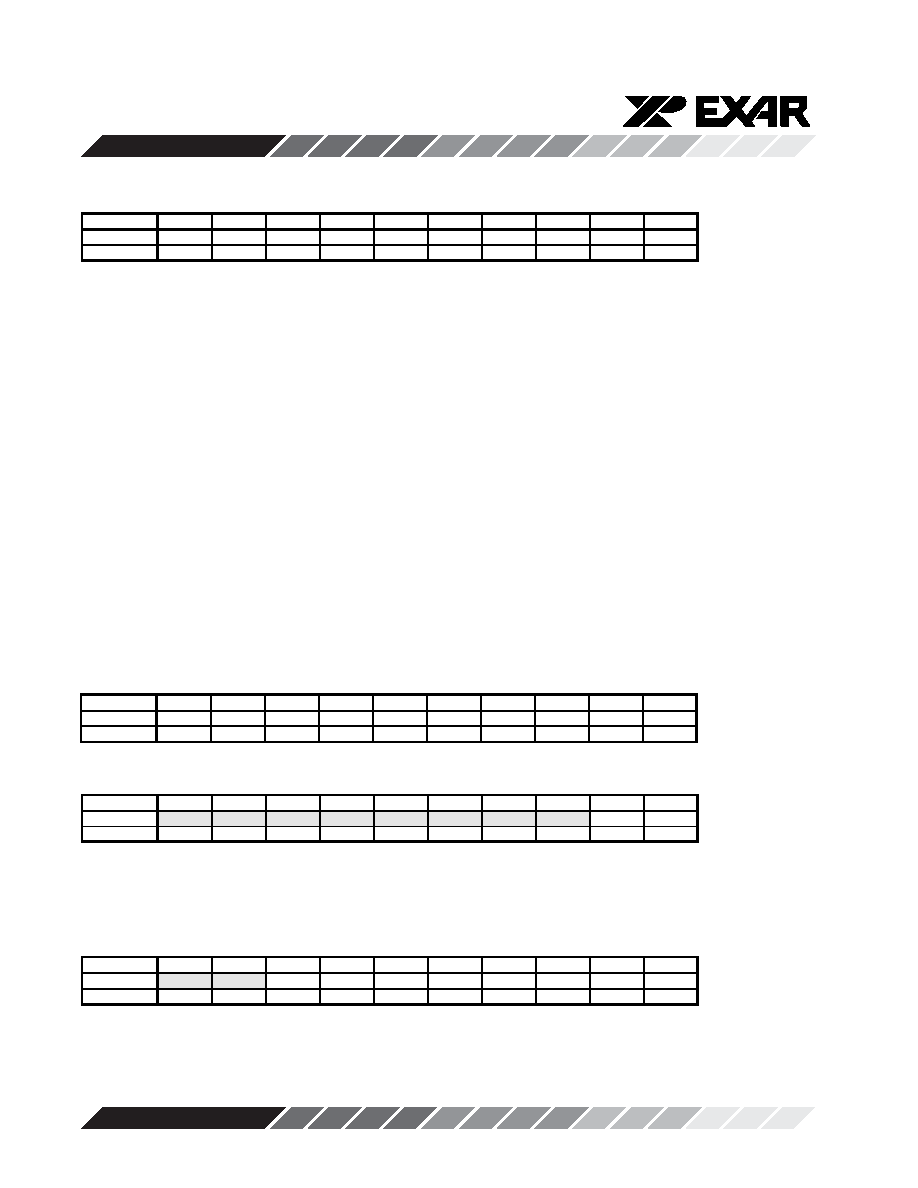

OB Lines

OBL[7]

OBL[6]

OBL[5]

OBL[4]

OBL[3]

OBL[2]

OBL[1]

OBL[0]

Default

0000000010

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Calibration

Avg[2]

Avg[1]

Avg[0]

Mode

LFrame

DNS[1]

DNS[0]

FastCal

Hold

ManCal

Default

1010011100

The Calibration register is used to set various options for the Black Level Offset Calibration.

Avg[2:0] set the number of OB pixels to average:

000 = 4 pixels,

100 = 64 pixels,

001 = 8 pixels,

101 = 128 pixels,

010 = 16 pixels,

110 = 256 pixels,

011 = 32 pixels,

111 = 512 pixels.

Mode=0, selects Line mode calibration (use OB pixels at start or end of each line).

Mode=1, do not use.

LFrame=0, selects Line mode calibration.

LFrame=1, do not use.

DNS[1:0] selects the Digital Noise Suppression filter setting:

00 = off,

10 = medium,

01 = narrow,

11 = wide.

FastCal=1, enables an option to speedup convergence of the calibration feedback loop.

Hold=1, stops all updates to the Coarse and Fine offset DAC accumulators.

ManCal=1, enables manual calibration. The offset DACs are set to the values in the CDAC and FDAC

registers.

See the Black Level Offset Calibration section for more information.

WaitA Register (Reg. 3, Address 000011)

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

WaitB

WL[1]

WL[0]

Default

0000000001

WaitB Register (Reg. 4, Address 000100)

The WaitA and WaitB registers are concatenated to make up the Wait register.

See OB Pixel calibration section for more information.

OB Lines Register (Reg. 5, Address 000101)

The OB Lines register is used by the Offset Calibration Logic to set the number of Optical Black lines used

for Calibration in the Frame Mode. Do not use.

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

WaitA

WL[11]

WL[10]

WL[9]

WL[8]

WL[7]

WL[6]

WL[5]

WL[4]

WL[3]

WL[2]

Default

0000000000

Calibration Register (Reg. 2,Address 000010)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRD98L63AIV-F | IC CCD DIGITIZER 12BIT 48TQFP |

| XRT71D00IQ-F | IC JITTER ATTENUATOR SGL 32TQFP |

| XRT71D03IV-F | IC JITTER ATTENUATOR 3CH 64TQFP |

| XRT71D04IV | IC JITTER ATTENUATOR 4CH 80TQFP |

| XRT8000IP-F | IC WAN CLOCK E1/E1 DUAL 18PDIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRD98L62EVAL | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開(kāi)發(fā)工具 XRD98L62 EVAL BOARD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類(lèi)型:ADC 工具用于評(píng)估:ADS130E08 接口類(lèi)型:SPI 工作電源電壓:- 6 V to + 6 V |

| XRD98L62ZEVAL | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開(kāi)發(fā)工具 Eval Board (Solder) XRD98L62AIV RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類(lèi)型:ADC 工具用于評(píng)估:ADS130E08 接口類(lèi)型:SPI 工作電源電壓:- 6 V to + 6 V |

| XRD98L63 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:CCD Image Digitizers with CDS, PGA and 12-Bit A/D |

| XRD98L63AIV | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:CCD Image Digitizers with CDS, PGA and 12-Bit A/D |

| XRD98L63AIV-F | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。