- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375007 > XCF16PFSG48C (XILINX INC) Platform Flash In-System Programmable Configuration PROMS PDF資料下載

參數(shù)資料

| 型號(hào): | XCF16PFSG48C |

| 廠商: | XILINX INC |

| 元件分類: | DRAM |

| 英文描述: | Platform Flash In-System Programmable Configuration PROMS |

| 中文描述: | 16M X 1 CONFIGURATION MEMORY, PBGA48 |

| 封裝: | LEAD-FREE, PLASTIC, TFBGA-48 |

| 文件頁數(shù): | 6/46頁 |

| 文件大?。?/td> | 525K |

| 代理商: | XCF16PFSG48C |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

Platform Flash In-System Programmable Configuration PROMS

DS123 (v2.9) May 09, 2006

www.xilinx.com

6

R

logic 0. IR[2] is unused, and is set to '0'. The remaining bits

IR[1:0] are set to '01' as defined by IEEE Std. 1149.1.

XCFxxP Instruction Register (16 bits wide)

The Instruction Register (IR) for the XCFxxP PROM is sixteen

bits wide and is connected between TDI and TDO during an

instruction scan sequence. The detailed composition of the

instruction capture pattern is illustrated in

Table 8, page 6

.

The instruction capture pattern shifted out of the XCFxxP

device includes IR[15:0]. IR[15:9] are reserved bits and are

set to a logic 0. The ISC Error field, IR[8:7], contains a

10

when an ISC operation is a success; otherwise a

01

when

an In-System Configuration (ISC) operation fails. The

Erase/Program (ER/PROG) Error field, IR[6:5], contains a

10

when an erase or program operation is a success;

otherwise a

01

when an erase or program operation fails.

The Erase/Program (ER/PROG) Status field, IR[4], contains

a logic 0 when the device is busy performing an erase or

programming operation; otherwise, it contains a logic 1. The

ISC Status field, IR[3], contains logic 1 if the device is

currently in In-System Configuration (ISC) mode; otherwise,

it contains logic 0. The DONE field, IR[2], contains logic 1 if

the sampled design revision has been successfully

programmed; otherwise, a logic 0 indicates incomplete

programming. The remaining bits IR[1:0] are set to

01

as

defined by IEEE Std. 1149.1.

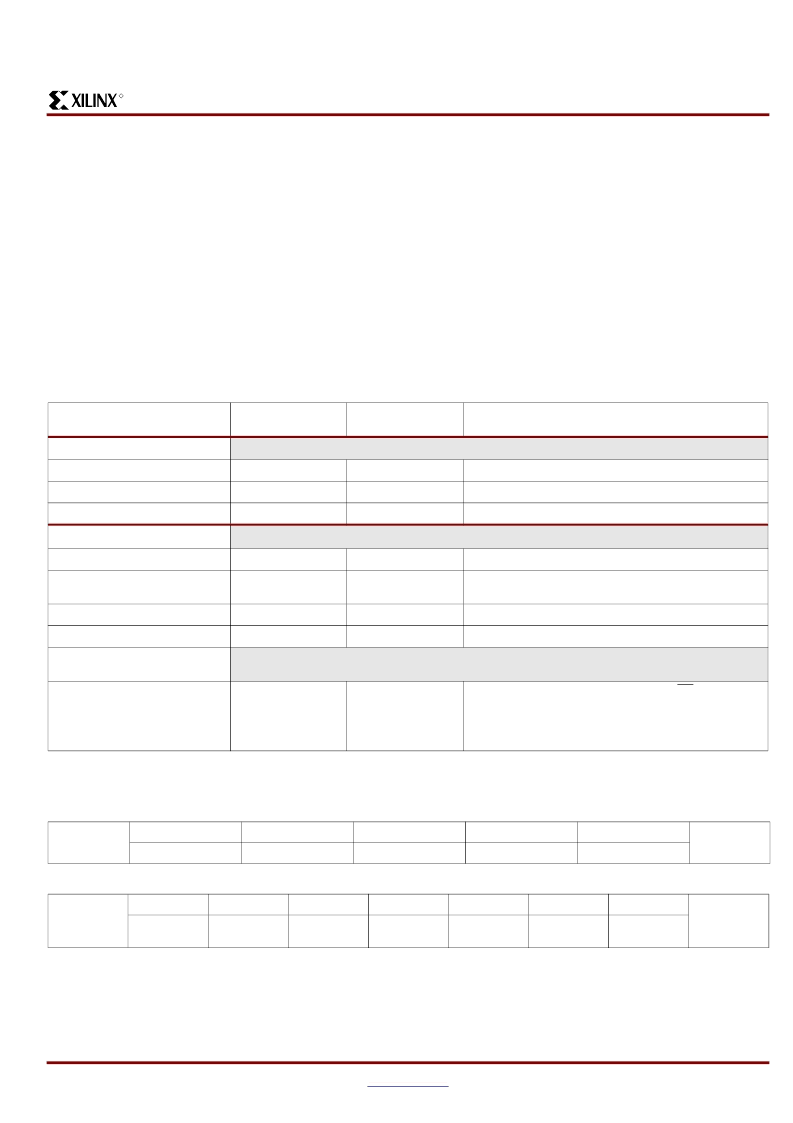

Table 6:

Platform Flash PROM Boundary Scan Instructions

Boundary-Scan Command

XCFxxS IR[7:0]

(hex)

XCFxxP IR[15:0]

(hex)

Instruction Description

Required Instructions

BYPASS

FF

FFFF

Enables BYPASS

SAMPLE/PRELOAD

01

0001

Enables boundary-scan SAMPLE/PRELOAD operation

EXTEST

00

0000

Enables boundary-scan EXTEST operation

Optional Instructions

CLAMP

FA

00FA

Enables boundary-scan CLAMP operation

HIGHZ

FC

00FC

Places all outputs in high-impedance state

simultaneously

IDCODE

FE

00FE

Enables shifting out 32-bit IDCODE

USERCODE

FD

00FD

Enables shifting out 32-bit USERCODE

Platform Flash PROM

Specific Instructions

CONFIG

EE

00EE

Initiates FPGA configuration by pulsing CF pin Low

once. (For the XCFxxP this command also resets the

selected design revision based on either the external

REV_SEL[1:0] pins or on the internal design revision

selection bits.)

(1)

Notes:

1.

For more information see

"Initiating FPGA Configuration," page 13

.

Table 7:

XCFxxS Instruction Capture Values Loaded into IR as part of an Instruction Scan Sequence

TDI

→

IR[7:5]

IR[4]

IR[3]

IR[2]

IR[1:0]

→

TDO

Reserved

ISC Status

Security

0

0 1

Table 8:

XCFxxP Instruction Capture Values Loaded into IR as part of an Instruction Scan Sequence

TDI

→

IR[15:9]

IR[8:7]

IR[6:5]

IR[4]

IR[3]

IR[2]

IR[1:0]

→

TDO

Reserved

ISC Error

ER/PROG

Error

ER/PROG

Status

ISC Status

DONE

0 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCF16PV | Platform Flash In-System Programmable Configuration PROMS |

| XCF16PVG | Platform Flash In-System Programmable Configuration PROMS |

| XCF16PVO48 | Platform Flash In-System Programmable Configuration PROMS |

| XCF16PVO48C | Platform Flash In-System Programmable Configuration PROMS |

| XCF16PVOG48 | Platform Flash In-System Programmable Configuration PROMS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCF16PFSG48C4039 | 制造商:Xilinx 功能描述: |

| XCF16PFSG48C4118 | 制造商:Xilinx 功能描述: |

| XCF16PV | 制造商:XILINX 制造商全稱:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

| XCF16PV048C | 制造商:Xilinx 功能描述: |

| XCF16PVG | 制造商:XILINX 制造商全稱:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。