- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374980 > XC3043L (Xilinx, Inc.) Field Programmable Gate Arrays(現(xiàn)場可編程門陣列) PDF資料下載

參數(shù)資料

| 型號: | XC3043L |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Field Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| 中文描述: | 現(xiàn)場可編程門陣列(現(xiàn)場可編程門陣列) |

| 文件頁數(shù): | 47/76頁 |

| 文件大?。?/td> | 731K |

| 代理商: | XC3043L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當前第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

R

November 9, 1998 (Version 3.1)

7-49

XC3000 Series Field Programmable Gate Arrays

7

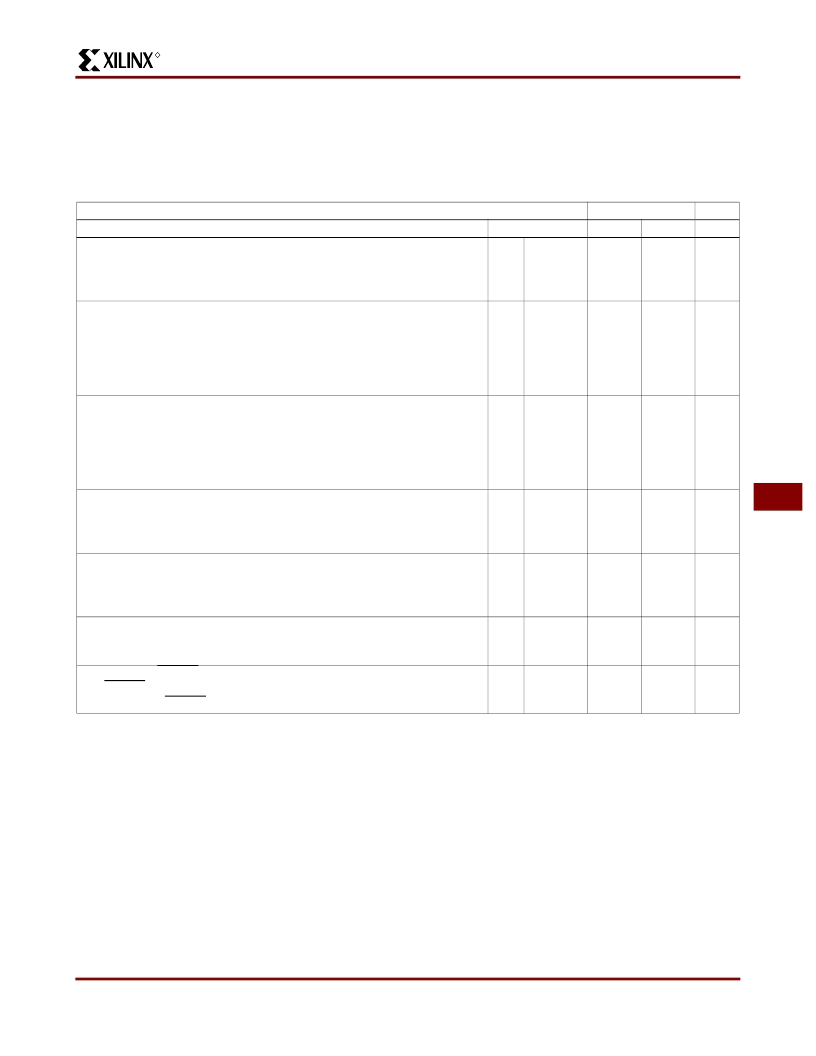

XC3000L CLB Switching Characteristics Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100%

functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark

timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more

detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used

in the simulator.

Notes:

1. Timing is based on the XC3042L, for other devices see timing calculator.

2. The CLB K to Q output delay (T

CKO

, #8) of any CLB, plus the shortest possible interconnect delay, is always longer than the

Data In hold time requirement (T

CKDI

, #5) of any CLB on the same die.

Speed Grade

Symbol

-8

Description

Min

Max

Units

Combinatorial Delay

Logic Variables

A, B, C, D, E, to outputs X or Y

FG Mode

F and FGM Mode

1

T

ILO

6.7

7.5

ns

ns

Sequential delay

Clock k to outputs X or Y

Clock k to outputs X or Y when Q is returned

through function generators F or G to drive X or Y

FG Mode

F and FGM Mode

Set-up time before clock K

Logic Variables

A, B, C, D, E

FG Mode

F and FGM Mode

Data In

DI

Enable Clock

EC

Hold Time after clock K

Logic Variables

A, B, C, D, E

Data In

DI

2

Enable Clock

EC

Clock

Clock High time

Clock Low time

Max. flip-flop toggle rate

Reset Direct (RD)

RD width

delay from RD to outputs X or Y

Global Reset (RESET Pad)

1

RESET width (Low)

delay from RESET pad to outputs X or Y

8

T

CKO

T

QLO

7.5

14.0

14.8

ns

ns

ns

2

4

6

T

ICK

T

DICK

T

ECCK

5.0

5.8

5.0

6.0

ns

ns

ns

ns

3

5

7

T

CKI

T

CKDI

T

CKEC

0

2.0

2.0

ns

ns

ns

11

12

T

CH

T

CL

F

CLK

5.0

5.0

80.0

ns

ns

MHz

13

9

T

RPW

T

RIO

7.0

7.0

ns

ns

T

MRW

T

MRQ

16.0

23.0

ns

ns

相關PDF資料 |

PDF描述 |

|---|---|

| XC3030A-6PQ100C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3142L-2PC84C | XTAL MTL T/H HC49/US |

| XC3142L-3PC84C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3142L-3TQ144C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3142L-3VQ160C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC3064 | 制造商:XILINX 制造商全稱:XILINX 功能描述:Logic Cell Array Families |

| XC3064100PC84C | 制造商:XILINX 功能描述:NEW |

| XC3064-100PC84C | 制造商:Xilinx 功能描述: 制造商:Xilinx 功能描述:Field-Programmable Gate Array, 224 Cell, 84 Pin, Plastic, PLCC |

| XC3064-100PC84I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC3064-100PG132M | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。