- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4285 > XA3S500E-4CPG132I (Xilinx Inc)IC FPGA SPARTAN-3E 500K 132CSBGA PDF資料下載

參數(shù)資料

| 型號: | XA3S500E-4CPG132I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 14/37頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3E 500K 132CSBGA |

| 標(biāo)準(zhǔn)包裝: | 360 |

| 系列: | Spartan®-3E XA |

| LAB/CLB數(shù): | 1164 |

| 邏輯元件/單元數(shù): | 10476 |

| RAM 位總計: | 368640 |

| 輸入/輸出數(shù): | 92 |

| 門數(shù): | 500000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 132-TFBGA,CSPBGA |

| 供應(yīng)商設(shè)備封裝: | 132-CSPBGA(8x8) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

DS635 (v2.0) September 9, 2009

Product Specification

21

R

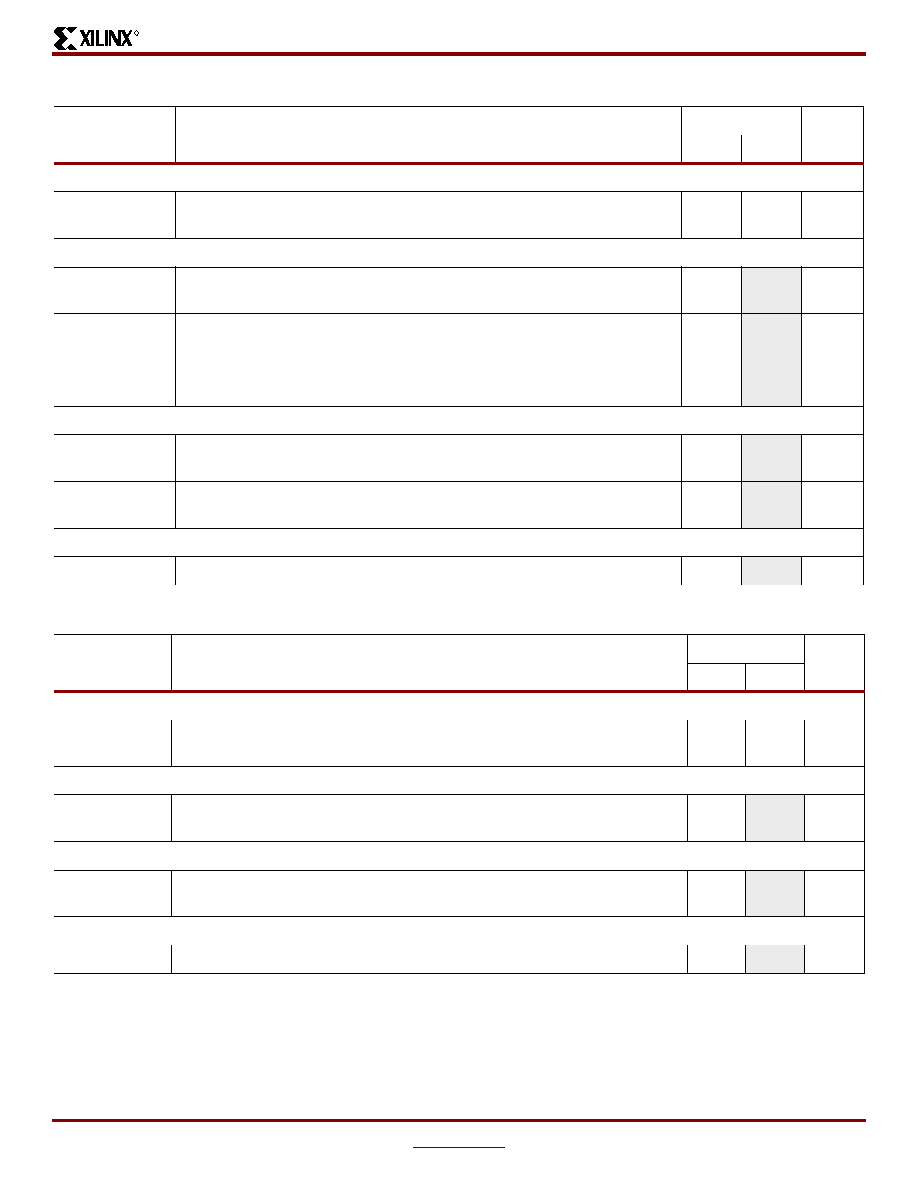

Table 21: CLB Distributed RAM Switching Characteristics

Symbol

Description

-4

Units

Min

Max

Clock-to-Output Times

TSHCKO

Time from the active edge at the CLK input to data appearing on the

distributed RAM output

-2.35

ns

Setup Times

TDS

Setup time of data at the BX or BY input before the active transition at the

CLK input of the distributed RAM

0.46

-ns

TAS

Setup time of the F/G address inputs before the active transition at the CLK

input of the distributed RAM

0.52

-ns

TWS

Setup time of the write enable input before the active transition at the CLK

input of the distributed RAM

0.40

-ns

Hold Times

TDH

Hold time of the BX, BY data inputs after the active transition at the CLK

input of the distributed RAM

0.15

-ns

TAH, TWH

Hold time of the F/G address inputs or the write enable input after the active

transition at the CLK input of the distributed RAM

0

-ns

Clock Pulse Width

TWPH, TWPL

Minimum High or Low pulse width at CLK input

1.01

-ns

Table 22: CLB Shift Register Switching Characteristics

Symbol

Description

-4

Units

Min

Max

Clock-to-Output Times

TREG

Time from the active edge at the CLK input to data appearing on the shift

register output

-4.16

ns

Setup Times

TSRLDS

Setup time of data at the BX or BY input before the active transition at the

CLK input of the shift register

0.46

-ns

Hold Times

TSRLDH

Hold time of the BX or BY data input after the active transition at the CLK

input of the shift register

0.16

-ns

Clock Pulse Width

TWPH, TWPL

Minimum High or Low pulse width at CLK input

1.01

-ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC6SLX16-3FTG256C | IC FPGA SPARTAN 6 14K 256FTGBGA |

| XC6SLX16-3CSG225C | IC FPGA SPARTAN 6 14K 225CSGBGA |

| AMC31DRYN-S13 | CONN EDGECARD 62POS .100 EXTEND |

| AMC31DRYH-S13 | CONN EDGECARD 62POS .100 EXTEND |

| HSC50DRAN | CONN EDGECARD 100PS R/A .100 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XA3S500E-4CPG132Q | 功能描述:IC FPGA SPARTAN-3E 500K 132CSBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FT256Q | 功能描述:IC FPGA SPARTAN-3E 256FPBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FTG256I | 功能描述:IC FPGA SPARTAN-3E 500K 256FTBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FTG256Q | 功能描述:IC FPGA SPARTAN-3E 500K 256FTBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4PQG208I | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。