- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372541 > XA-SCC (NXP Semiconductors N.V.) CMOS 16-bit communications microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | XA-SCC |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | CMOS 16-bit communications microcontroller |

| 中文描述: | 的CMOS 16位微控制器的通信 |

| 文件頁數(shù): | 29/42頁 |

| 文件大小: | 229K |

| 代理商: | XA-SCC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary specification

XA-SCC

CMOS 16-bit communications microcontroller

1999 Mar 29

29

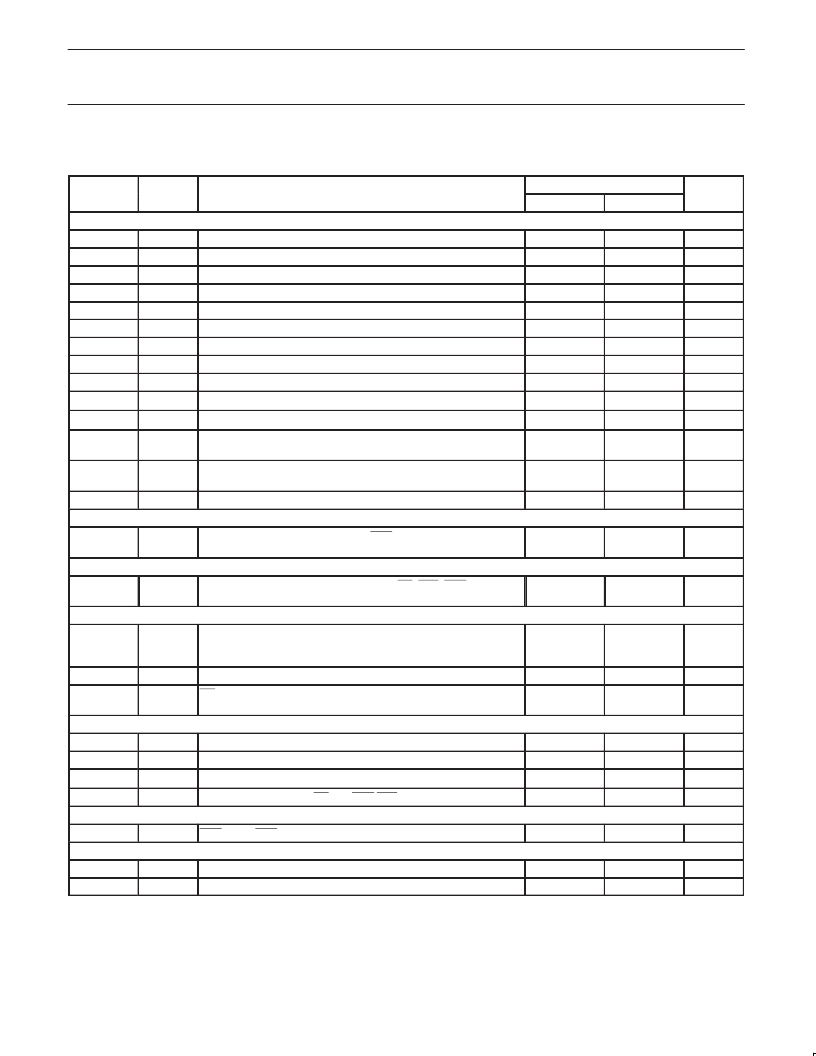

PRELIMINARY AC ELECTRICAL CHARACTERISTICS (5.0V

V

DD

= 5.0V

10%, T

amb

= –40 C to +85 C (industrial)

10%)

1

LIMITS

SYMBOL

All Cycles

F

C

FIGURE

PARAMETER

MIN

MAX

UNIT

System Clock Frequency

0

30

MHz

t

C

25

System Clock Period = 1/F

C

XTALIN High Time

33.33

–

ns

t

CHCX

t

CLCX

t

CLCH

t

CHCL

t

AVSL

t

CHAH

t

CHAV

t

CHSH

t

CHSL

t

CODH

25

t

C

* 0.5

t

C

* 0.4

–

–

ns

25

XTALIN Low Time

–

ns

25

XTALIN Rise Time

5

ns

25

XTALIN Fall Time

–

5

ns

All

Address Valid to Strobe low

Address hold after CLKOUT rising edge

9

t

C

– 21

1

–

ns

All

–

ns

All

Delay from CLKOUT rising edge to address valid

Delay from CLKOUT rising edge to Strobe High

9

–

1

1

25

ns

All

21

ns

All

Delay from CLKOUT rising edge to Strobe Low

9

19

ns

26

ClkOut Duty Cycle High (into 40pF max.)

(See

Warning

Note 5 on page 31.)

t

CHCX

–7

t

CHCX

+3

ns

t

CPWH

13, 14, 16,

20, 21, 22

CAS Pulse Width High

t

C

– 12

–

ns

t

CPWL

13, 21

CAS Pulse Width Low

t

C

– 10

–

ns

All DRAM cycles

t

RP

24

RAS precharge time, thus minimum RAS high time

8

(n * t

C

) –16

note 8

–

ns

Generic Data Read Only

t

AHDR

9, 16

Address hold (A19–A1 only, not A0) after CS, BLE, BHE rise at end

of Generic Data Read Cycle (not code fetch)

t

C

–12

–

ns

Data Read and Instruction Fetch Cycles

t

DIS

9, 10,

12–14, 16,

17, 20, 21

Data In Valid setup to ClkOut rising edge

25

–

ns

t

DIH

t

OHDE

Data In Valid hold after ClkOut rising edge

2

0

–

ns

10, 12, 13,

16, 20, 21

OE high to XA Data Bus Driver Enable

t

C

– 14

–

ns

Write Cycles

t

CHDV

t

DVSL

t

SHAH

t

SHDH

Refresh

t

CLRL

Wait Input

t

WS

t

WH

NOTE:

1. See notes after the 3.3V AC timing table.

Clock High to Data Valid

–

25

ns

Data Valid prior to Strobe Low

t

C

– 23

t

C

– 25

t

C

– 25

–

ns

11, 16

Minimum Address Hold Time after strobe goes inactive

–

ns

Data hold after strobes (CS and BHE/BLE) high

–

ns

21

CAS low to RAS low

t

C

– 15

–

ns

24

WAIT setup (stable high or low) to CLKOUT rising edge

20

–

ns

24

WAIT hold (stable high or low) after CLKOUT rising edge

0

–

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XA1024 | Temperature Sensor(Frequencies Range Between 2 And 30 MHz)(溫度傳感器(頻率范圍: 2至 30 MHz)) |

| XA979 | Temperature Sensor(Frequencies Range Between 2 And 30 MHz)(溫度傳感器(頻率范圍: 2至 30 MHz)) |

| XAG30 | XA 16-bit microcontroller family 32K/512 OTP/ROM/ROMless, watchdog, 2 UARTs |

| XAM1214-130 | RF POWER TRANSISTORS L-BAND RADAR APPLICATIONS |

| XB0ASB03A1BR | SCHOTTKY BARRIER DIODE 500MA 30V TYPE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XA-SK-AUDIO | 制造商:XMOS Ltd 功能描述:SLICEKIT AUDIO SLICE CARD |

| XA-SK-E100 | 制造商:XMOS Ltd 功能描述:10/100 ETHERNET SLICE CARD |

| XA-SK-GPIO | 制造商:XMOS Ltd 功能描述:GPIO SLICE CARD |

| XA-SK-ISBUS | 制造商:XMOS Ltd 功能描述:INDUSTRIAL SLICE CARD |

| XA-SK-SCR480 | 制造商:XMOS Ltd 功能描述:DISPLAY SLICE CARD |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。